Other Parts Discussed in Thread: UC3843, UCC28951, UCC28950, LM5036, UCC3895, UCC2895, LM5045

Hello.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello.

Hi Patty,

Using two TL494's in that configuration seems very unreliable. I think it would be difficult to synchronize the two parts. If they become out of sync for even 1 or 2 pulses the regulator will more than likely destroy itself. I imagine TI has solutions based on a single IC that will do exactly what you require. Start with WEBENCH or search the available Reference Designs for something you can adapt to your needs.

Regards,

Eric

Thanks for your reply Eric Reicher.

pls offer me an alternative solution if I were to use tl494 since this pwm ic is readily available. The other ic i have is uc3843

Hi Patty,

Both of those ICs are relatively old, slow, bipolar controllers. I'm not sure they're up to the task.

If you want to control synchronous rectifiers on the secondary side please consider LM5036, UCC28950, or UCC28951.

You can obtain complete design recommendations from WEBENCH. Or take a look at TI's offering of Reference Designs.

Regards,

Eric

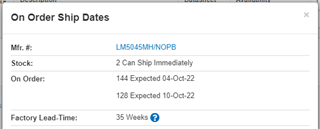

can the ucc3895/ucc2895 also do the job?, I can see that the ucc28950/51 are out of stock

Hi Patty,

The UCC2895/3895 (20-pin devices) do not have the synchronous rectifier output pins. The UCC28950 or UCC28951 (24-pins) seem to be a good choice and offer a lot of design support (Excel tools, simulation tools, app notes, etc.)

Where can you order from? Can you request samples from TI directly?

Eric

I usually use mouser electronics to buy components, but if one can order from TI then it would be better

I see. LM5045 is another possibility. This is a bit older (National Semi) part that may be more widely available and has a good datasheet, Excel based design tool, and Pspice model.

Mouser only has 2 at this time, but will have more next month.

Would this satisfy your project requirements?

Eric

I will wait for the ucc28950/51 so that I can also use it in AC/DC applications. For now I will just reduce my output current to 15A then use output diodes instead of mosfets then use a push pull converter with tl494. Kindly explain to me the remainder of my questions. From question 3 onwards.

Replies to your questions:

3) Create an NPN/Zener based LDO from Vout.

4) By "emitter" do you mean pins 9 and 10? The emitter will follow close to wherever the collectors (pins 8 and 11) are connected.

5) I don't believe this problem occurs when synchronizing multiple TL494's as shown in section 4.2.2. The "problem" was pointed out in the next section, 4.2.3, Synchronizing to a Master Clock.

6) I don't know.

7) Seems plausible.

8) I'm not sure what you mean by "reduce the strain on the input capacitors". Simple use enough input capacitors to support the expected RMS current.

Eric

Do you not want an auxiliary winding on secondary side? I don't think it's possible without loosing input/output isolation.

Eric

My main purpose of wanting to use secondary side regulation was so that I can use two tl494ics. But now I will be using one. Can I use a start up resistor like what is normally done in UC3843 when designing a flyback converter then use an auxiliary winding in the primary side. Can I do this with a push pull converter?

Yes, that should work. Here is a design with TL494 doing what you described.

Eric

Thanks a lot for the assistance.

Kindly explain question 7 further. If I use peak current limiting configuration in my design instead of output current limiting, do I have to worry about transformer flux imbalance? If I use peak current limiting to track the input output current

Some additional comments on Question 7:

When operating a double ended topology in VMC, you should add a DC blocking cap in series with the transformer primary to prevent flux imbalance in the event a DC bias builds up in the core. Operating in peak CMC naturally takes care of this because the current is sensed and adjusted on a cycle by cycle basis. No transformer primary blocking cap is required when operating in peak CMC.

Giving instructions on magnetics design is beyond the scope of E2E. TI is in the business of selling controllers.

Regards,

Eric

If I use the tl494 for peak current limiting should I treat the controller as a current mode controller?

My last question is when will the ucc28950/51 be available?

Hi Patty,

The TL494 uses the voltage ramp at the CT pin to determine the duty cycle, so I would call that voltage mode control. Peak current limiting simply sets a boundary for the current in the power stage to prevent destruction.

Sorry, I do not know when UCC28950/51 will be available. I have no insight into the supply chain for any of TI's products.

Eric

which controllers that are available that I can use for double ended topologies. similar to ucc28950/51

Here is a link to all the double ended controllers offered by TI. You can narrow down the results by choosing features from the menus on the left.

If you have additional questions please post a new thread.

Eric