Hi :

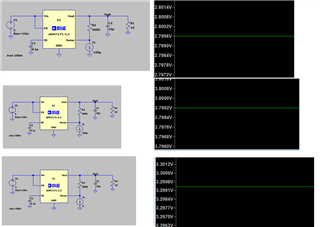

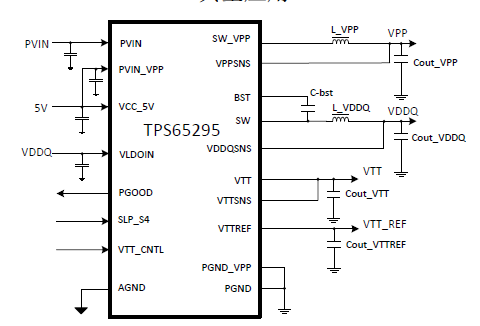

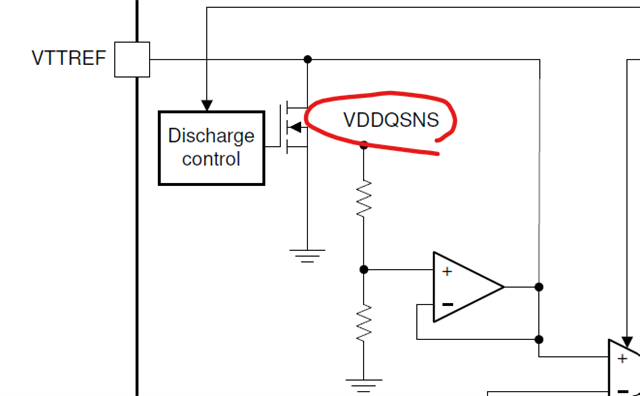

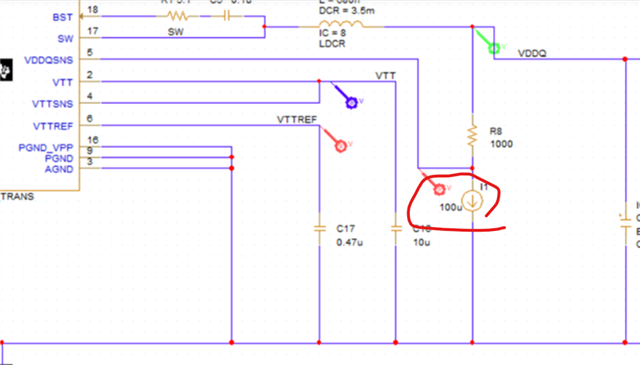

I am using TPS65295 IC for our DDR4 power solution.

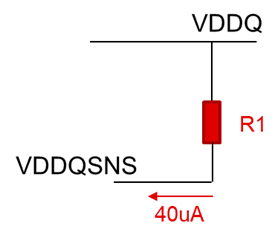

I would like to vary the VDDQ supply +/-3% (1.2V +/-3%) to characterize the DDR4 controller performance at corner voltage scenario.

Is there a way to change this beyond the typical limit of 1.2V ?

best regards

Shamanth