Hi Team,

1. I was reading about datasheet of TPS62903-Q1. In 9.2.2.5.1 paragraph about output capacitor, here says 'Using higher value has a tighter DC output accuracy'. I'm confused that why and how the value of output capacitor influences DC accuracy? Is there any reason about loop gain as we all know high DC loop gain causes a high DC accuracy?

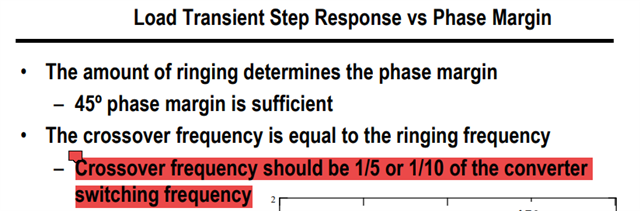

2. About compensation loop design in VM control mode Buck converter, some documents shows about we should set crossover frequency on 1/5~1/10 switching frequency which is a typical engineering experience. I wonder why crossover frequency(bandwidth) is related with switching frequency and what's the performance goal if we set crossover frequency as this?

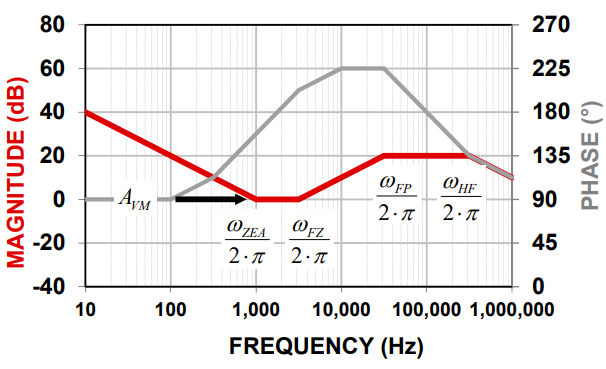

3. About the design of TypeⅢ compensator, the bode plot is as below. There is a wHF pole in the plot which is the higher frequency pole. I saw a documents about how to put this pole that it's set to half switching frequency. Could u please kindly explain why ? :)

Thanks a lot!

Best regards!

Victoria