Other Parts Discussed in Thread: UCC27624

Hi together,

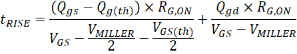

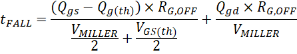

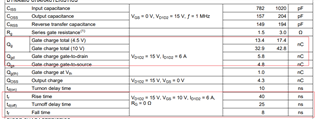

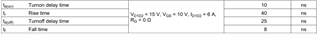

I want to design a switching circuit witch shall ensure the rise time is the same as the fall time. But look through a lot of NMOS datasheets. The values of rise time and fall time are quite different.

Since the process of MOS's turn-on and turn-off all have relate to charging time for Ciss, Why is there such a big difference in rise time and fall time.

Thanks!

Zhiyao