Other Parts Discussed in Thread: TIDA-01095, TIDA-080008

Hi,

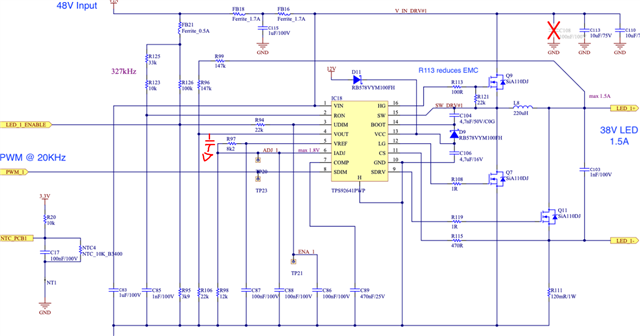

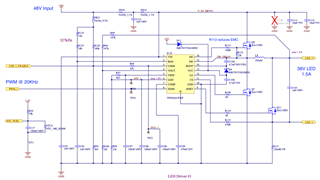

we have an issue with a TPS92641 LED driver. The schematic is this:

Supply Voltage is 48V, LED String Voltage is 38V, LED Current is 1.5A

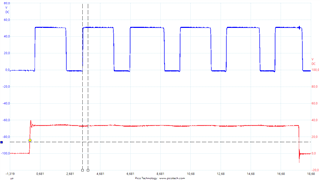

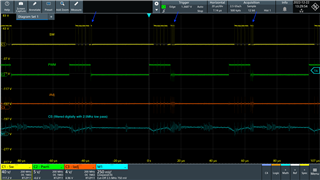

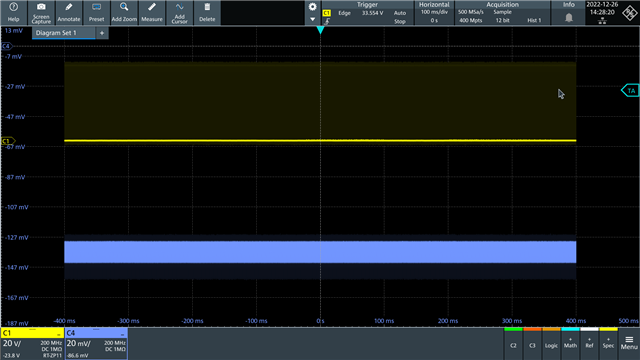

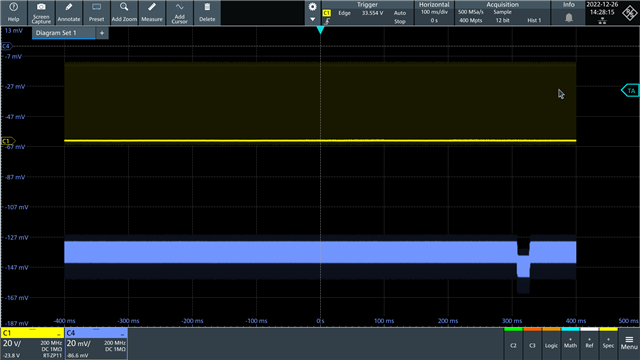

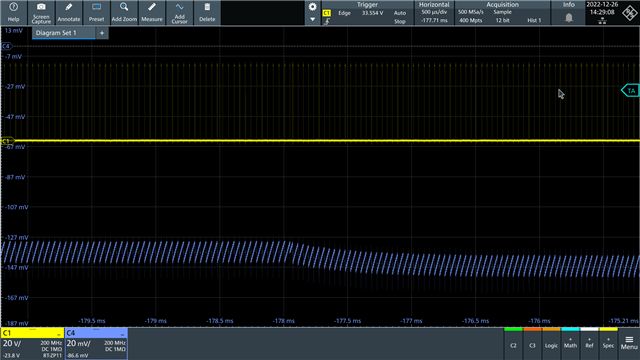

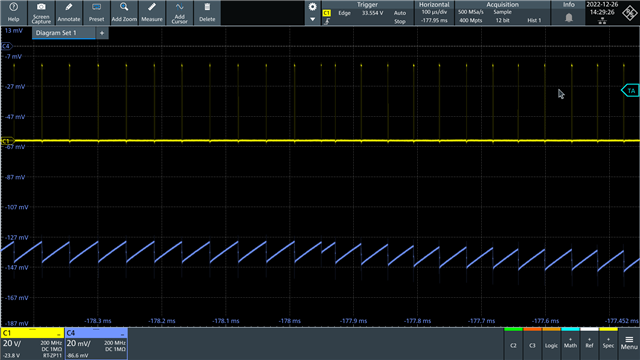

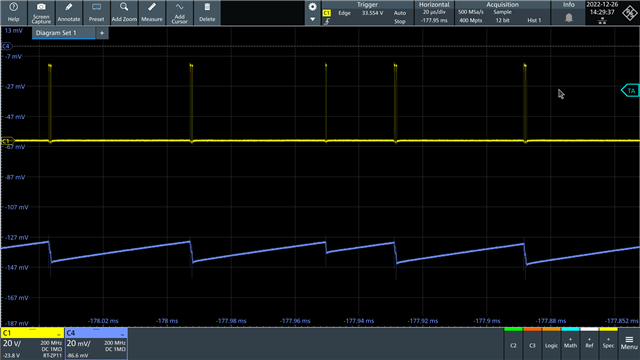

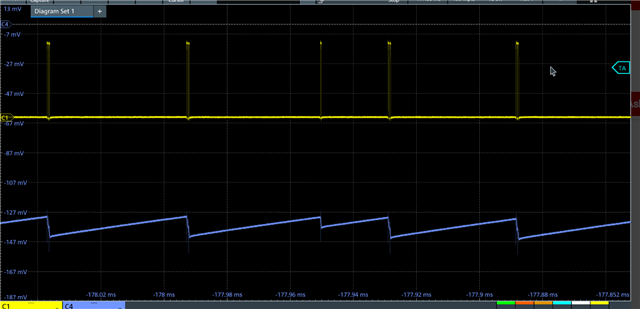

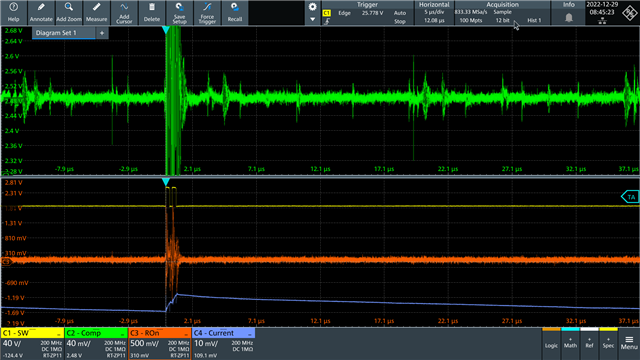

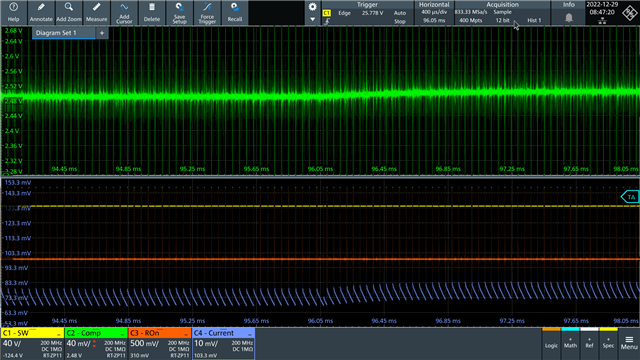

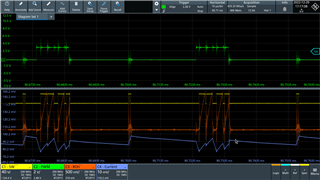

We have discovered flicker problems which occur at specific duty cycles when using the Shunt FET dimming. Our PWM frequency is 20KHz. When we linearly go through the entire dimming range we can observer multiple duty cycle settings which produce visible flicker (e.g. 2-4 points from 0-100%, for example 50%, 71%).

We have narrowed it down to the drivers current regulation which seems to oscillate at certain settings. We have tried to change a lot of thing already, but nothing really did solve the issue. The only change that happens is that the dimming level where it happens moved to different values.

Our tests so far:

- Higher value for CS resistor R115 (22k)

- Smaller inductor (68uH, 100uH)

- Bigger Capacitor for Comp C89 (1uF)

- Different driver frequencies up to 600KHz

- Different Output Capacitor C103 (limited options as Q11 gets too hot, if value goes beyond a few dozen nF)

- Bigger Sense resistor R111 (150mR - slightly reduces current already)

- Slowing down of FET transistors by changing R108, R113

Looking forward to your help as we are running out of options to save this design.

Best regards,

Thomas