Hi team,

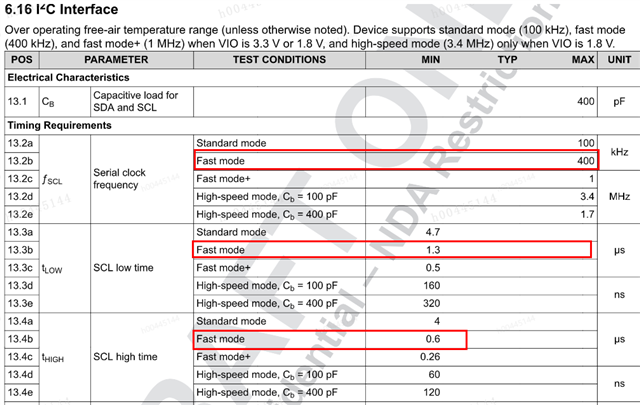

According to datasheet, the max SCLK frequency is 400k(fast mode), if we assumed that duty cycle is 50%, then the min SCLK high/low time should be 1/400k*50%=1.25us. However, Min SCLK time is 1.3us for logic low and 0.6us for logic high. These timing requirements conflict with each other.

What is the timing requirement of I2C?

B&R

Lijia