Other Parts Discussed in Thread: BQ25713

Hello TI,

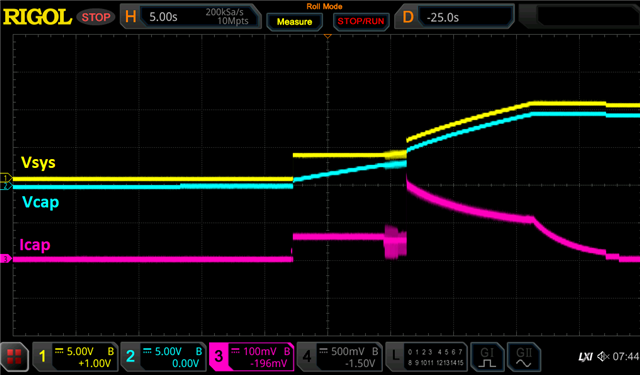

Just wanted to confirm some numbers for the SOA with this pfet. We are using the bq25713 to charge a supercap and have copied the EVM implementation with a difference of using a 2mOhm sense resistor on the batfet for faster charge up times. Our charge up time is about 22 seconds. During initial charge up when the supercap is depleted it must pass through the saturation region of the FET as it charges up to reach vsys which I set to 3 volts. Once it reaches vsys I then charge it up to 10 volts. Looking through the data for the current given by the BQ I made some calculations with regards to power and SOA and wanted to have confirmation that we are not exceeding the ratings of the PFET.

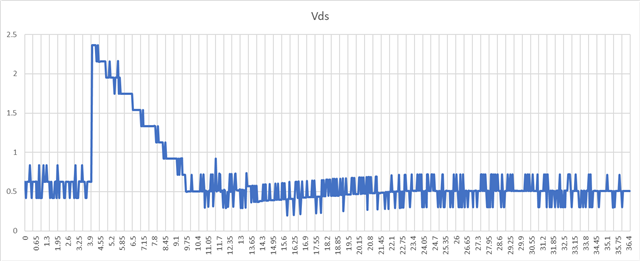

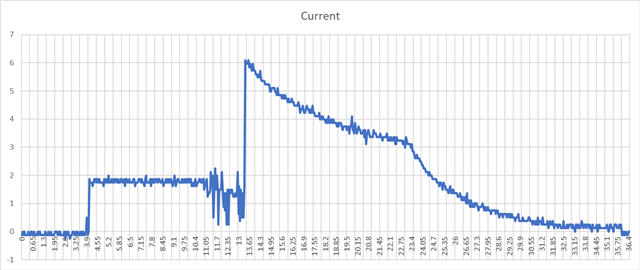

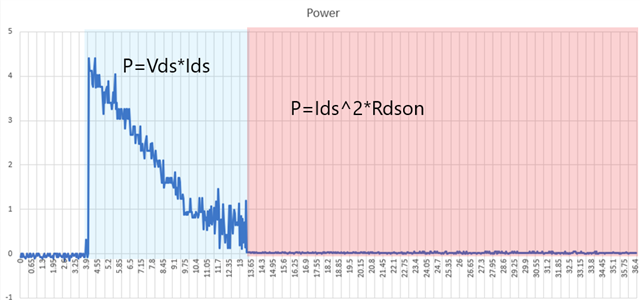

Exporting that data I calculated the power drop across the pfet:

Using these numbers I get a max power at initial charge up when Vds=2.36 and Ids=1.865 amps which gives 4.41 watts. This number is below the red line for DC in the safe operating area however it exceeds the first maximum power rating on the datasheet. Do these calculated figures look correct?