I did some test yesterday. I have some questions about ISO5451's DESAT protection mechanism.

Phenomenon:

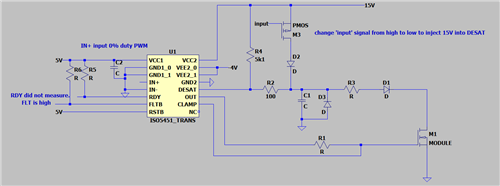

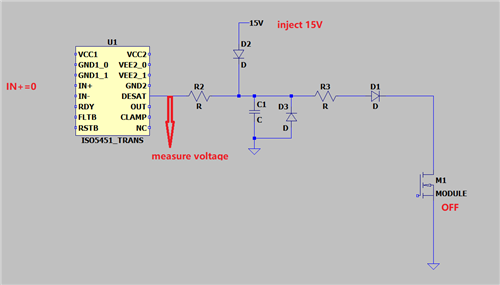

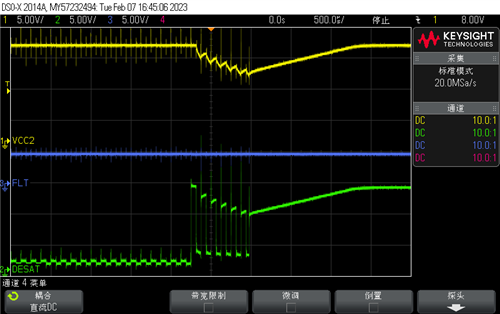

I forced IN+ to low, then injected 15V into the DESAT pin through an external supply via a resistor and a diode, after that measured the voltage of DESAT pin and FLT pin refer to the diagram below. I noticed that the DESAT pin is vibrating and the FLT pin is high refer to the waveform below.

Diagram:

Waveform:

Yellow line is VCC2; Blue line is FLT; Green line is DESAT.

Questions:

1.Is that mean during the power module shutdown or say the IN+/OUT is low, the DESAT function is inactive?

2.The DESAT pin has an internal mos, according to my understanding, during the power module is off, the DESAT pin is kept low internally by turn on the internal mos, the internal current source is switched off, is that right?

3.Could you explain why the waveform of DESAT pin is like that? Because of the turn on and turn off of the internal mos?