Hello, I am using the UCC28065 in a 115VAC, 730W PFC application. I have noticed something curious about the phase interleave.

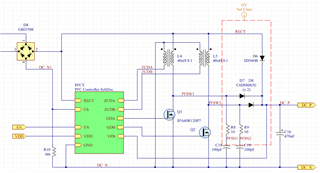

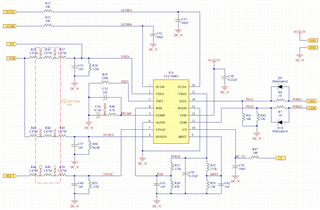

The application circuit is generally similar to the eval board, with smaller inductors to operate at higher power and frequency. See below:

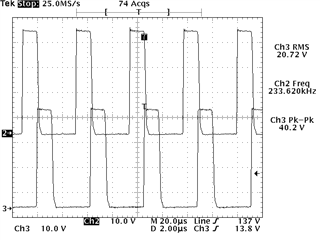

VDD is 13V. In the present test, Q1 and Q2 are SIHA105N60EF-GE3. The drain waveforms (PFSW1, PFSW2) look like so:

(Note: using 10x probes.) As you can see, the phase interleave is not 180 degrees. The inductors were measured and match within 5% of each other. Please advise.