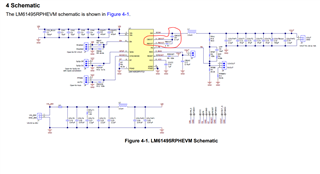

Other Parts Discussed in Thread: LM61495RPHEVM, ,

Hi team,

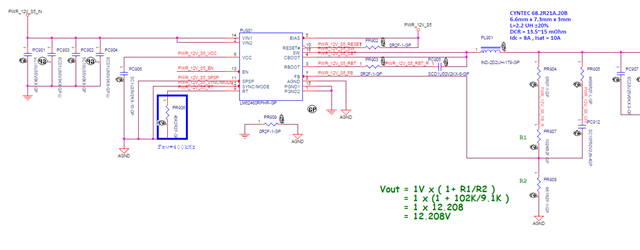

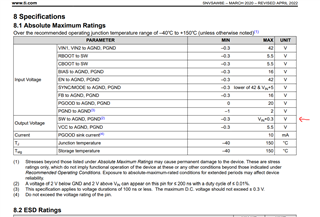

my customer mistaken the Cboot connection as you can see in the schematic here.

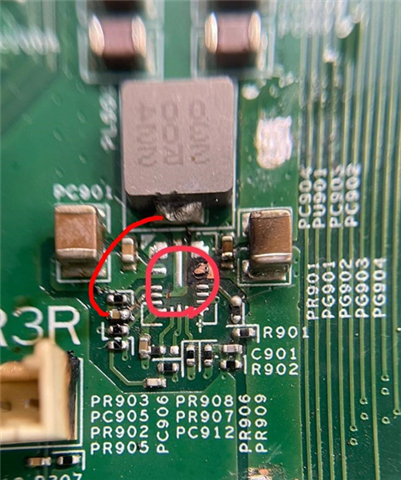

they tried to re-work on the board with single-core wire ,

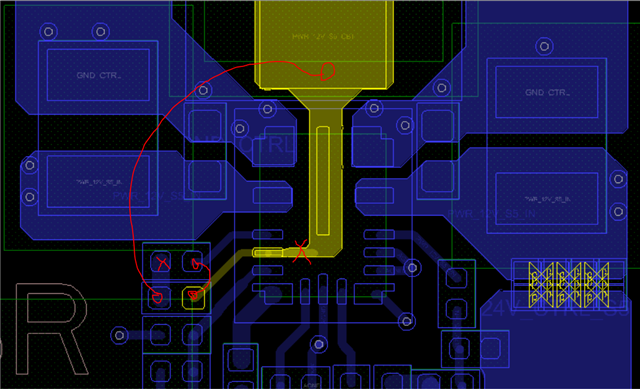

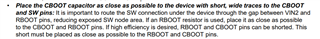

1. they first cut off the connection between the SW and Cboot

2. they use a wire to connect Rboot pin and Cboot pin

3. last, they use another long, thin one core wire to connect Cboot cap to SW.

but the Vin pin damaged right after they test full-load transient, is there anything we miss during the re-work?

is the long, thin one core wire for connection acceptable here?