Other Parts Discussed in Thread: BOOSTXL-TPS650861

Hello James Steenbock

Hope you remember me and the issues that we had discussed in above chat previously very long ago.

In the last message, I had mentioned that we shall build a new PCB with TI suggested changes and test it and provide feedback.

Finally, we build the PCB with TI suggested changes and tested it. But unfortunately, when we turned ON the board, PMIC was still in Power fault state. As usual we continued to debug the issue which caused the power fault in this PMIC. Below are our observations in CASE1 and CASE2,

CASE1:

1) We verified input & output rails and found to be correct VSYS=12V, LDO3P3=3V3, LDO5P0 =5V0, Vref=1V2 and V5ANA=5V0.

2) Then we started to debug the BucK1-6, VTT and LDOA1-A3 and found that PMIC was in power fault state.

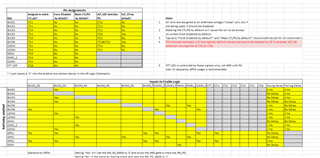

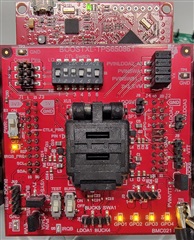

3) We also wanted to check if the IC from reel had any fault, to test this we used TI BOOSTXL-TPS650861 Evaluation board | TI.com. With this we can provide CTL1 to 6 inputs to start the PMIC sequence and check the respective rails for pre-programmed PMIC IC TPS65086401RSKT. as per our design we need to provide only 3 inputs to CTL pins (CTL1, CTL6 and CTL4 in same order or sequence)

4) when we provided CTL1 and found that associated power rails were up without any power Fault and GPO1 was ON

5) when we provided CTL6 and found that associated power rails were up without any power Fault and GPO2 & GPO3 was ON (But as per sequence only GPO3 was supposed to be ON)

6) when we provided CTL4 and found that PMIC entered into power fault state and so we just removed CTL4 to see if PMIC recovered from power fault and yes it did.

Summary: A brand new PMIC IC TPS65086401RSKT from the reel when tested with Eval board was showing power fault. To confirm this behavior, we removed the input CTL4 on our newly build board and found that PMIC was able to recover from power fault although the rails associated with the CTL4 were not up.

CASE 2:

From the case history we had concluded that, if the required caps were not provided for unused pins like (LDOA1, LDOA2, LDOA3, SWA1, SWB1 &SWB2) then we can use a custom OTP programmed PMIC with Part # TPS65086100 and disable these pins. We did try this and following were the observations,

1) We programmed our custom OTP into Blank PMIC IC TPS65086100 and replaced it with our pre-programmed IC on our newly build boards to mitigate the above CASE1 issue.

2) After replacing the IC with OTP IC and did a power ON, initially it seems all the rails were working, but when we did a power cycle, we saw PMIC went to power fault state.

Buck1: 1V8 without power fault

Buck1: 1V8 with power fault

3) after providing a time gap of about 10mins and then when we turned ON the board the PMIC was seen functioning normal without any power fault. But didn't stay for long and just entered again into power fault state.

Summary: the issue that we are facing here is, every time we do a power cycle to OTP burned PMIC we need to provide a delay of around 10mins or so. and sometimes it may be more. Hence case2 is also not helping us to resolve issues faced in case1. We are seeing some inconsistence with respect to PMIC's behavior.

Since this build of boards were for customer delivery, we are not able to delivery any hardware till now and struggling to resolve this PMIC related issue. Hence, I would request you to please support us in resolving this issue as its turn out to be a critical issue and blocking our delivery to customer.

The schematics of PMIC is already with you.

Old case details: TPS650864: Troubleshooting PMIC behavior used to power Xilinx ZU3. - Power management forum - Power management - TI E2E support forums

Let me know if you have any other questions.

Best regards,

Sandeep P