Hi Guys,

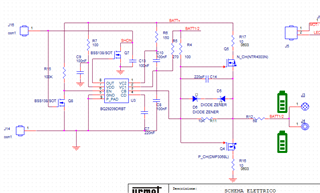

I'm cheking my application with BQ29209 about overvolage protecion condition.

During charge the OUT pin go high at 4295 mV but when the Vbad decrease of 20/30mV the OUT pin go low; in the data sheet is showed an hysteresis min of 200mV.

It is wrong the data sheet ?

Thank You

Best Regards

Stefano