Hi TI Expert,

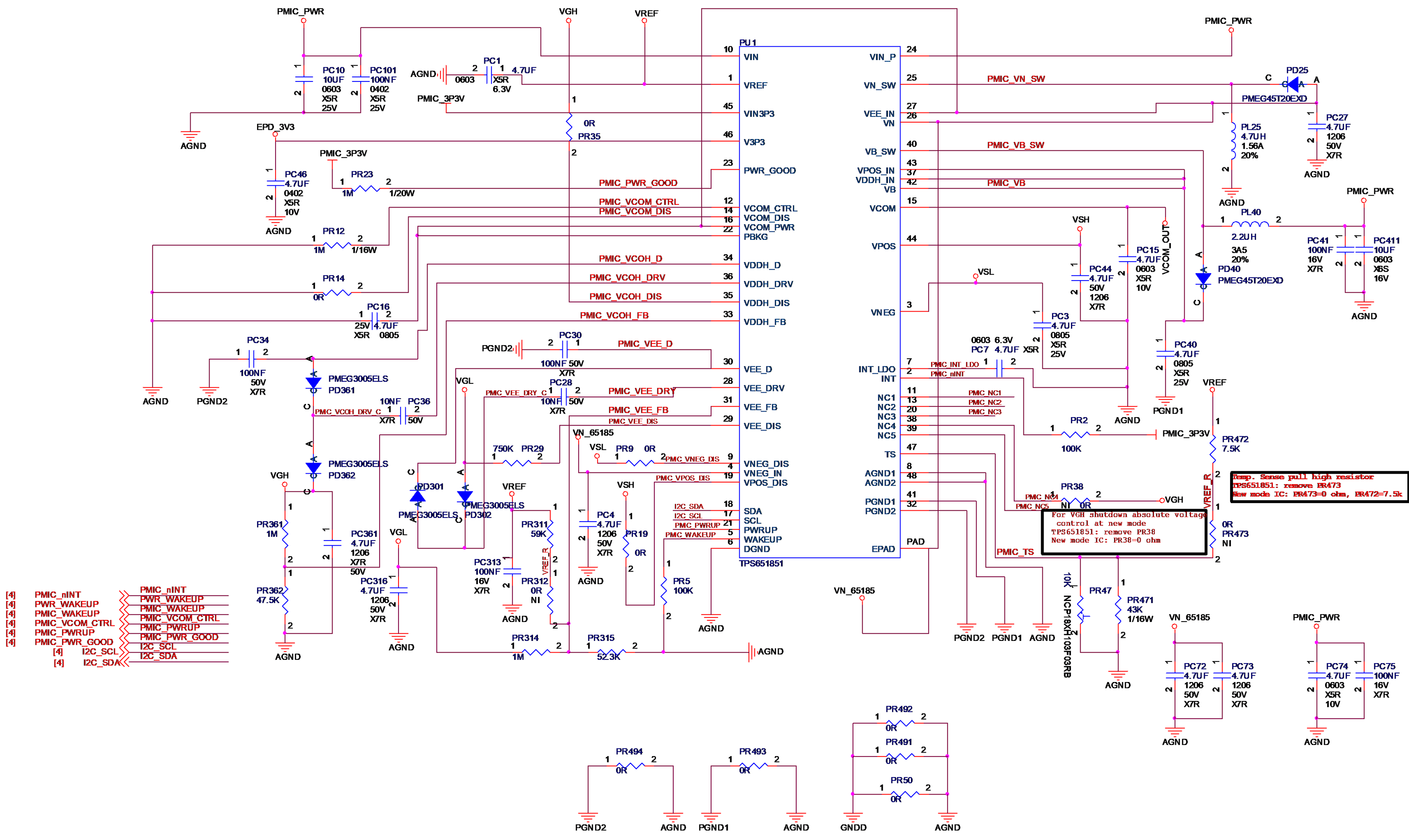

Currently we use the PMIC TPS651851(Full MPN is TPS651851RSLR) designed in a display board, please refer to below screenshots for the schematics, the timing measurement we find the time delay between VEE(VGL) & VNEG(VSL) is not enough to meet spec requirement.

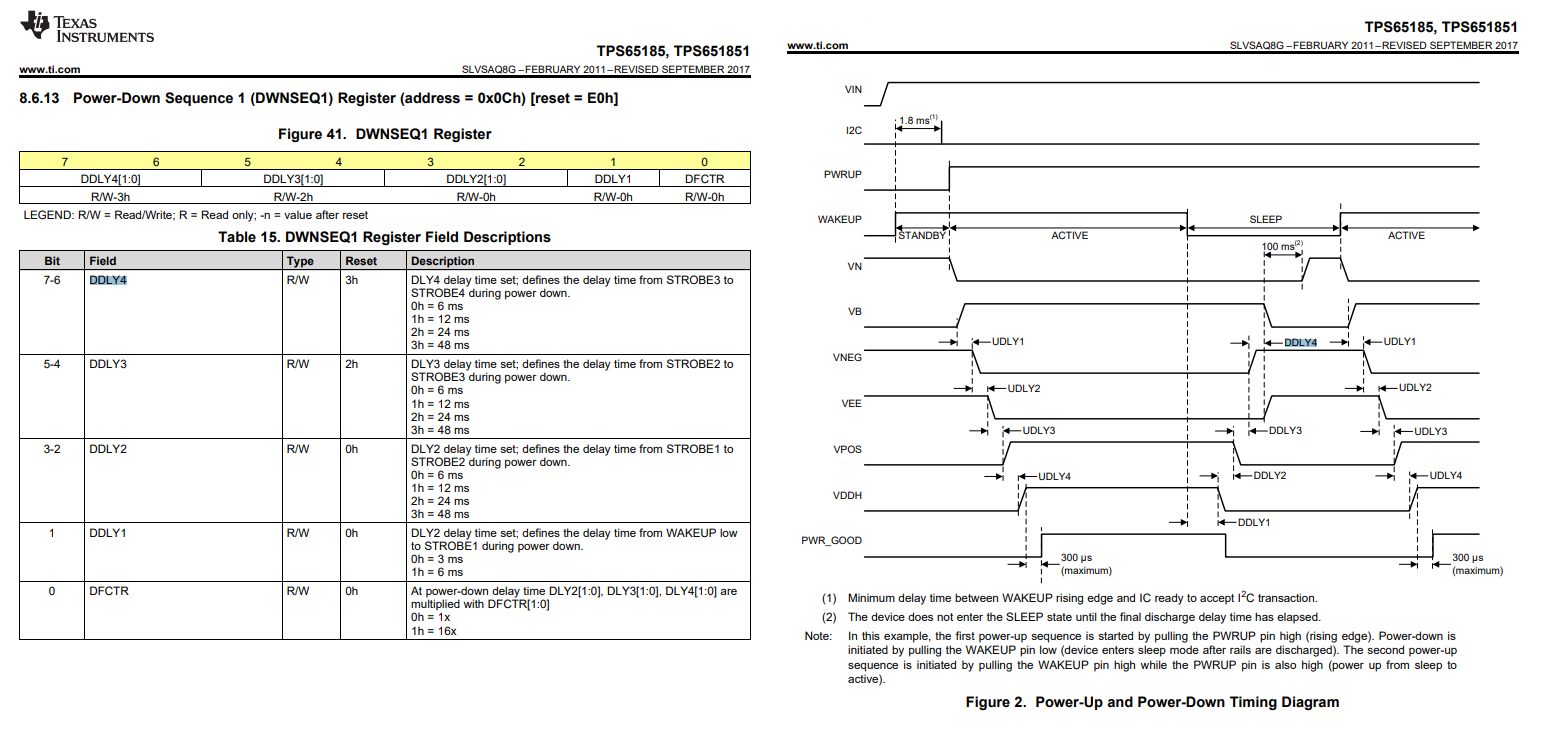

From the datasheet described, we know the DDLY4 & DFCTR could be adjusted by the Power-Down Sequence 1 (DWNSEQ1) Register via the I2C bus to extend the delay time, per the schematics and datasheet it looks the time delay probably can only be adjusted through I2C by this register, but would like to double confirm if the understanding is correct? Or is there any others to adjust the time delay?

Besides, it looks TPS651851 doesn’t have register to adjust the voltage rail’s power down falling slew rate, would like to know that does TPS651851 have hardware pin or its peripheral component can adjust the VEE’s / VNEG’s voltage power down’s falling slew rate? Maybe resistor on the discharge pin or any others?

Thank you.

Measured time delay of VEE(VGL) & VNEG(VSL) - CH1 : VNEG , CH2 : VEE

(would like to extend the time delay and falling down slew rate)

Power-down sequence 1(DWNSEQ1) register : DDLY4 between VEE & VNEG

Schematics: