Supervisor selection for DSP TMS320F28377:

The VDDIO and VDD of DSP are powered by 5V/3.3V LDO1( ADP3339AKCZ-3.3) and 3.3V/1.2V LDO2(AMS1117-1.2) respectively.

The minimum output of LDO1 is Vcc1_min= 3.2373V (-1.9% of 3.3V).

The minimum output of LDO2 is Vcc2_min=1.152V(-4% of 1.2V).

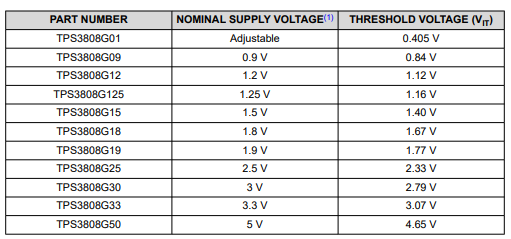

According to the output range of the LDOs and the recommended working supply range, Is it OK to choose TPS3808G09 and TPS3808G33 as voltage supervisors?

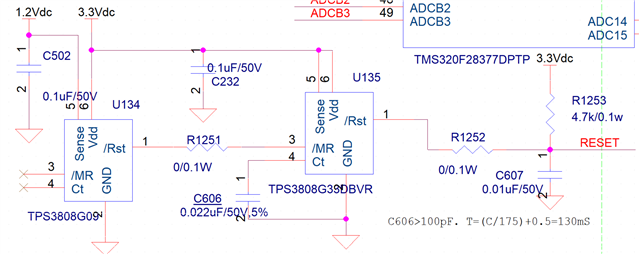

The picture above shows the circuit related to voltage monitoring, the reset delay time Td is 130mS(decided by C606) ,

Can this design meet the reset requirements and power supervisor requirements of the DSP?