Other Parts Discussed in Thread: IPG-UI

Hi,

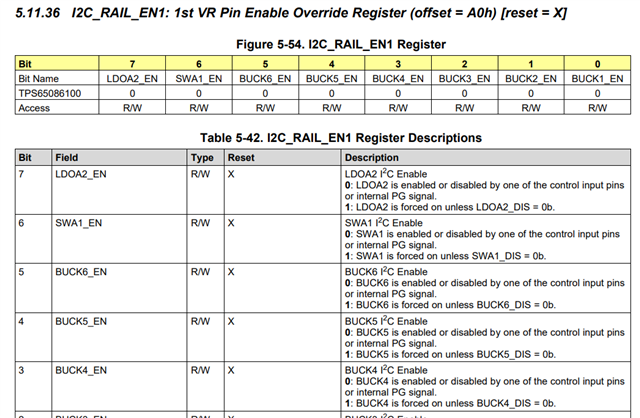

I am trying to control power on sequence for CPU with CTL pin, after configuring program mode in address 0X38, but it didn't output correctly. In the end, we found also a need to configure register 0XA0 each to high in address 0X5E, then allow control power output by CTL pin. According to the datasheet described register 0XA0 should configure each to low, then can control power output by CTL pin. Am I missing some detail?