Other Parts Discussed in Thread: ISO7731,

Hello,

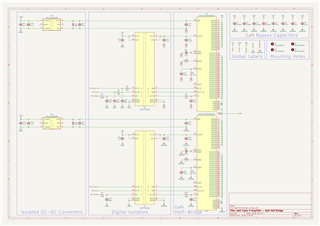

I would like to request a review for the design of a half-bridge board at a desired switching frequency of 500 kHz and output maximum power of 500 W at 8-ohm loudspeaker for a class D audio power amplifier.

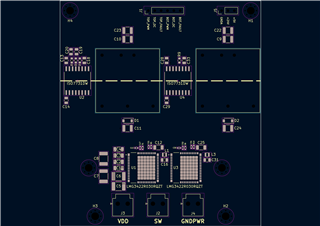

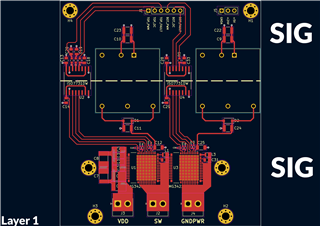

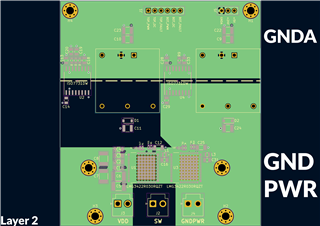

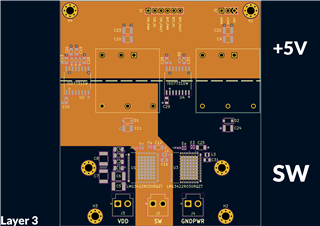

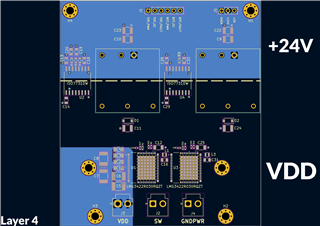

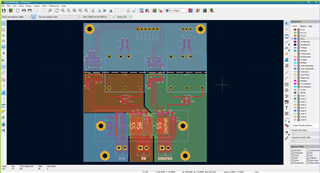

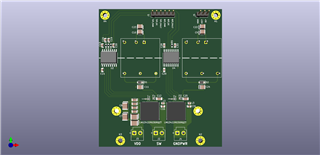

The PCB consists of four layers, with each layer labeled in the figures attached.

Each copper layer is 1 oz thickness, with board thickness of 1.6 mm. The design requires the use of two isolated DC-DC converters (TRACO POWER - THL 15-2412WI) as well as two digital isolators (ISO7731). Due to that, the board is divided across the middle into two separate sections.

The temperature pin (TEMP) of the switching devices is intentionally ignored in the PCB design.

Attached below are the pictures for each layer, and the complete half-bridge schematic.

4846.Schematic.pdf

4846.Schematic.pdf

Thank you.