Good morning,

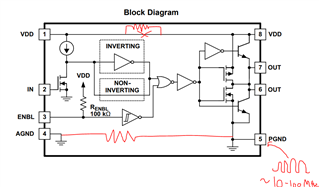

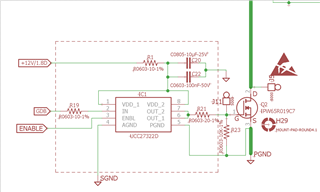

the UCC27322 circuit in SO-8 version has 2 pins for PGND and SGND.

What do you recommend for the connection of these 2 pins on the PCB?

In my opinion, it is necessary to connect PGND directly and as short as possible to the source of the MOS and SGND to the ground plane of the control signals, but where to connect the common point of these 2 GNDs for a low noise and best practice?

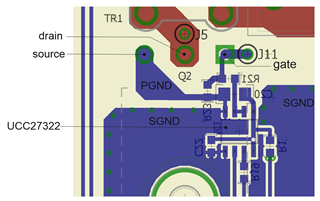

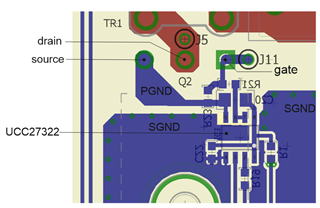

I am attaching the part of the driver schematic concerned and the 2 possibilities for connecting the GNDs (pin 4 and 5), thank you in advance for your advice.

Red layer is top layer, blue is bottom layer, the UCC27322 is in bottom layer

Best regards.

JY