Other Parts Discussed in Thread: LMR33630,

Hi,

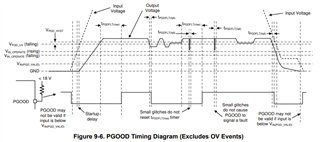

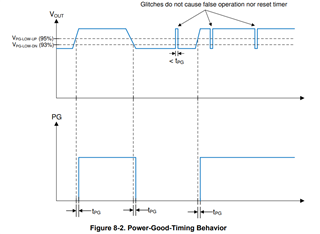

I am confused why 6A LM61460 PG deglitch time is much lower than LMR33630's PG deglitch time? And why LM61460's rising deglitch time is much higher than LMR33630? Any consideration? I do not think it has effect to actual power up or reset. Thanks!

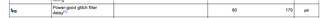

LMR33630 both 60-170us for PG rising and falling

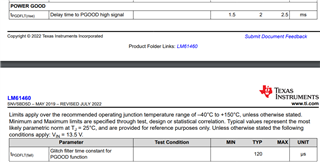

LM61460 Rising 2ms falling 120us

-A