Other Parts Discussed in Thread: AM2732

Hi ,

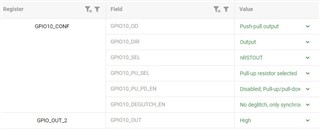

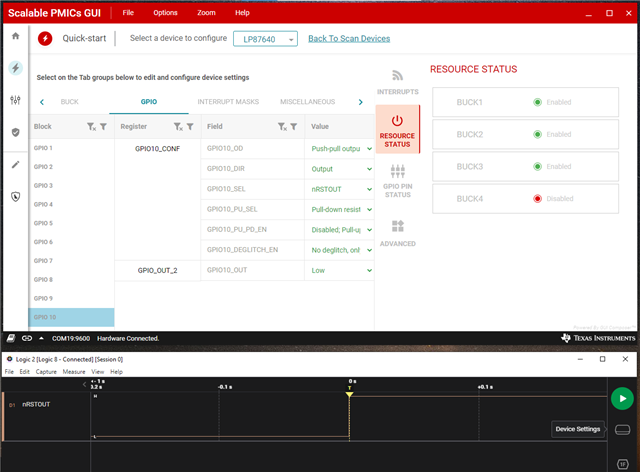

I want to use LP876242Q1EVM(BMC085A) to a generate a nRESET signal for the external system .

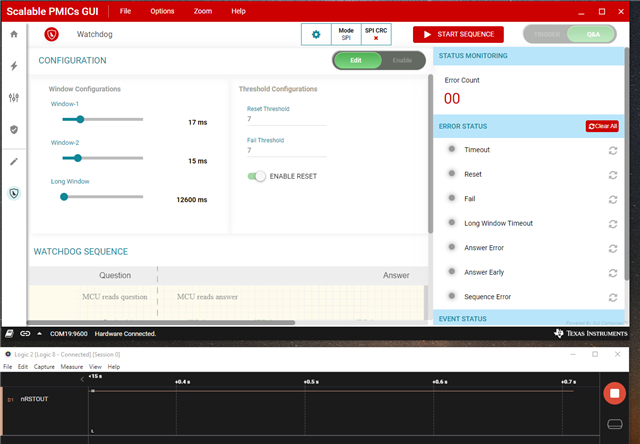

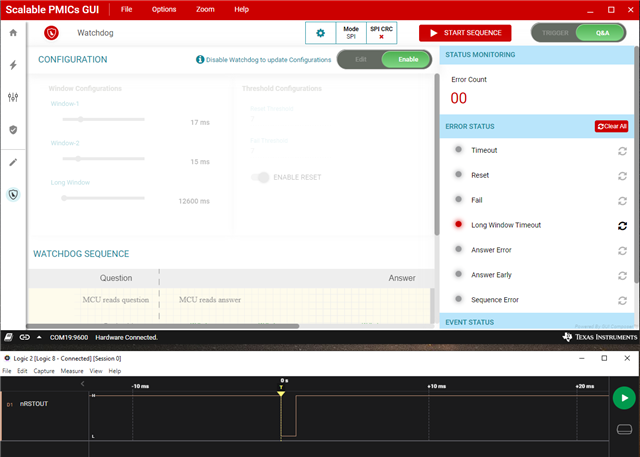

By enabling or disabling the watchdog, a reset signal can be generated to trigger an external system to reset.

Can you pls guide me how to config the watchdog for that purpose?

Thanks,

Simon