Other Parts Discussed in Thread: TPS3899

Hi team!

Using the TPS3420 as a reset pushbutton where a reset is performed by holding the power button for about 10s typically. Sometimes, there is very little current drawn on Vsys, so the rail stays high and chips are not power reset over this 10s.

This is where the TPS3420 looks ideal. it can discharge the Vsys rail after the power button has been held for many seconds.

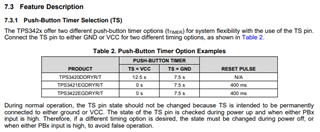

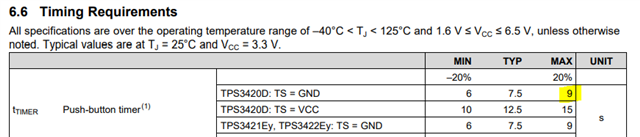

The TPS3420 looks like an ideal solution but the maximum specification is 9s. In this application, Ttimer can never be above 8s. IF above 8s, we miss a critical window where battery FET is disconnected.

Any thoughts or possible solutions around this? We are open to chip recommendations or circuit ideas

Thanks,

Cameron