Other Parts Discussed in Thread: TLV3501

Hello:

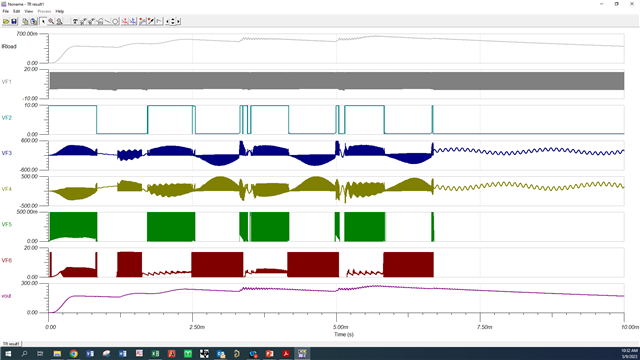

I can make the TINA model work using UC1846 for a SEPIC converter but it is not giving correct results.

The grand scheme here is to explore how it will work with feedback and then optimize the L & C values.

I suspect I have all the wrong semiconductors- it is almost impossible to guess what to select from TINA TI list of devices.

If I can email you the model, is it possible to help select proper devices from some list you might have that are more convenient to choose from?

Or use some artifact to make it work?

Any help will be appreciated.

r