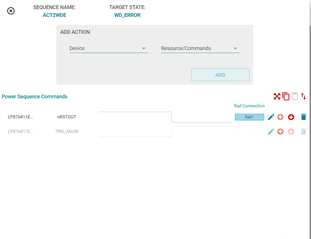

I have assigned GPIO10 for nRESETOUT\ function.

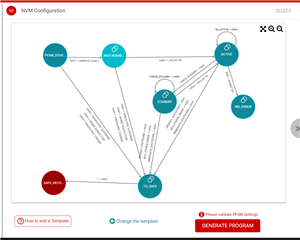

I want to assert this signal when Watchdog error is encounted. But I do not want to power down the chip.

If I assert this signal when WD_ERROR is encountered, Is it possible for another master to de assert this nRESETOUT via an I2C register write ?