Other Parts Discussed in Thread: LM5123EVM-BST,

Hello,, thanks for taking the time to look at this. I've spent about a week trying to figure out this issue and could use some help.

I've designed a test board using the LM51231QRGRRQ1 which is based on the LM5123EVM-BST evaluation board. The values on the schematic (attached) are the current values being tested.

The design is operating in FPWM mode with the expectation that it would output 24VDC. It's on a 2-layer board that has not been optimized for EMI and we've already done a design review to tighten up ground loops and remove thermal relief on pads and vias. The prototype is being tested with a 10 ohm resistive load.

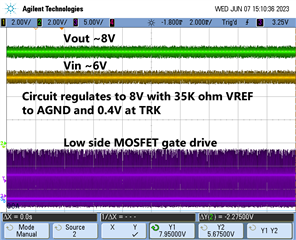

The VREF resistance to AGND is 35K ohm, the TRK voltage is set for 0.4V, and VREF is 1.0V. The actual measured resistance with a HP34401A multimeter is 34.886K ohms. TRK and VREF voltages were verified. This should set the output voltage to 0.4V*60 = 24V. However, the actual output is 8.0V indicating the "Lower VOUT Range" of 0.4V*20 (section 7.3.7 of the LM51231-Q1 October 2022 datasheet).

The circuit goes into output bypass mode at 8.5V and operates normally at 8.0V, UVLO range is set between 6-7V.

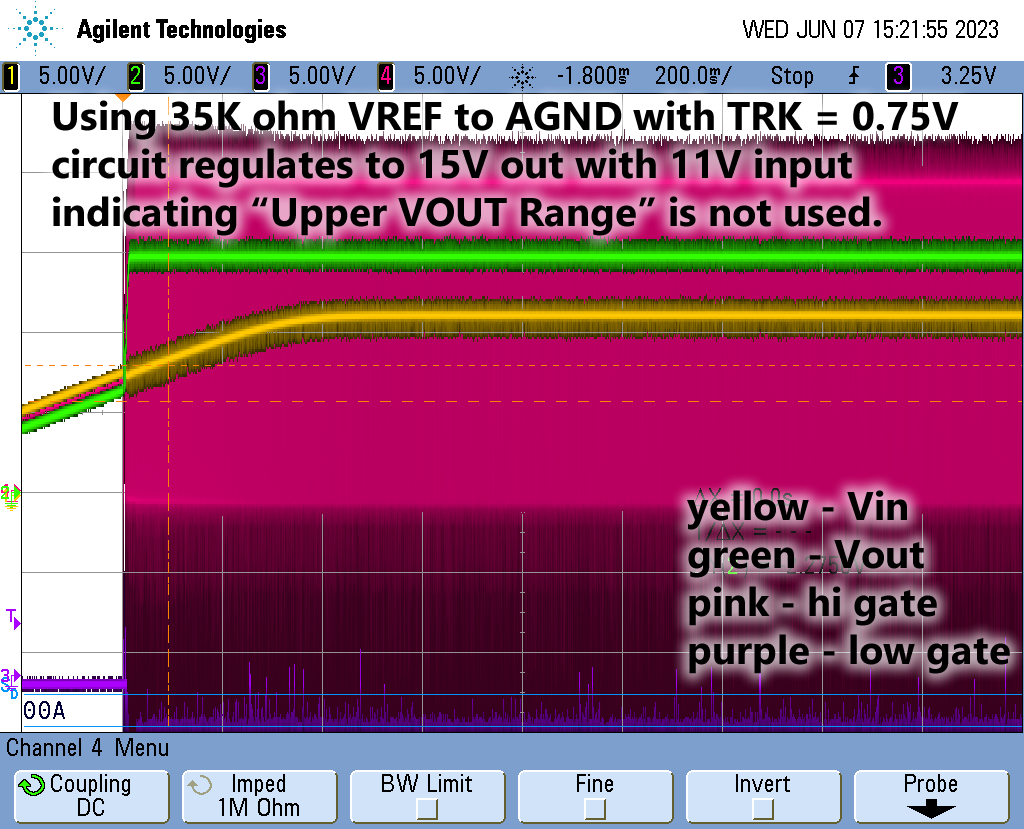

Changing the voltage divider from VREF to TRK to AGND to 6.8K and 21K sets the TRK voltage to 0.75V and the supply operates is enabled at 7V and has a regulated output of 15V (20*0.75).

It seems that regardless of the resistors used to set the output voltage the device is not using the "Upper VOUT Range". This leads me to believe something is going wrong during Configuration Mode (datasheet 7.4.1.2), or the datasheet is wrong.

I've done considerable testing including removing MOSFETS and inductor from the LM5123EVM-BST board and using them on my board. I've added input and output capacitance, I've tested resistors that would enable the "Lower VOUT Range" to see if the datasheet resistor values were swapped. The output regulated voltage is still TRK voltage*20.

Here's what I found:

1. Using 35Kohm for VREF to AGND and 0.4V for TRK the circuit will not configure VOUT to be 0.4V*60. With 16V supplied as the input voltage the circuit will begin active operation as the input exceeds UVLO at around 6V. It will continue attempting to regulate the output to 8V (0.4*20, not 0.4*60) until the input supply reaches over voltage protection at about 8.5V and then enter FPWM bypass mode. Shortly thereafter, as the input continues to rise the, the circuit turns off high and low MOSFETs and the output is VIN - MOSFET internal diode drop.

You would expect this operation if the resistance from VREF to AGND was 65Kohm (datasheet examples section 6.5). But not if the resistance from VREF to AGND is 35K ohms.

2. Changing the resistors from VREF to AGND to sum 30Kohm ensuring that the VREF to AGND resistors are not marginally outside the 35Kohm range in the datasheet has no impact. Vout is still regulated to TRK voltage * 20 and not TRK voltage * 60.

3. Changing the input voltage to 11V and setting the TRK voltage to 0.75 with a total of 28K ohms between VREF and AGND results in the power supply regulating a VOUT of 15V from the VIN of 11V . This again indicates that the IC is not using the "Upper VOUT Range" described in the datasheet.

Possible causes:

1. Something on my test board is causing configuration mode to read the VREF to AGND resistance wrong and it's either reading the "Low VOUT Range" or just defaulting to it.

2. The LM51231-Q1 datasheet is wrong, or incomplete and not indicating changes between the LM51231-Q1 and the LM5123.

3. There's a functional difference between the LM51231-Q1 I'm using and the LM5123 on the evaluation board. The evaluation design does regulate to 0.4*60 with 35K ohms between VREF and AGND.

VOUT Range".

+

+

Step-Up Supply r1_0.PDF