Hello,

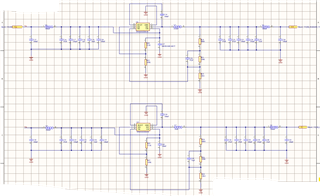

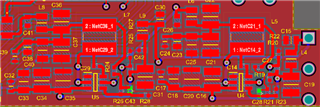

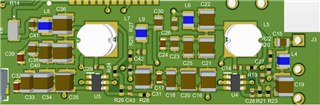

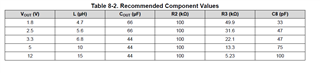

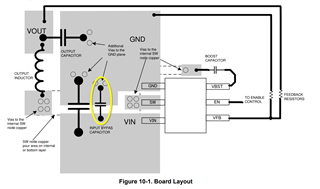

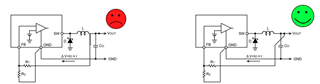

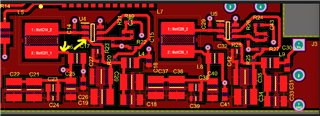

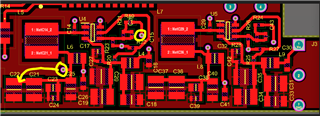

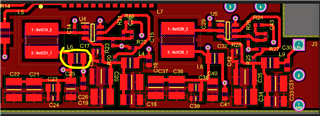

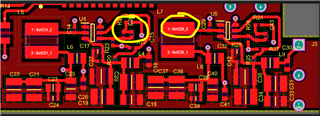

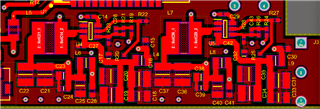

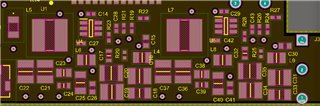

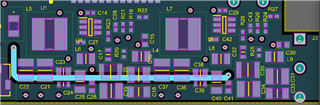

I have used two TPS54302 chips in my design to generate two voltage sources 5V DC and 3V3 DC from a common source Vin ( range from 7V DC to 24V DC, 3A).

I have done several tests and see that I can obtain 5V DC and 3V3 DC with some ripples ( around 40mV on 3V3 and around 120mV on 5V).

The problems that I have noticed are:

1- I cannot draw more than around 200mA from these voltage sources.

2- Drawing currents from each source (5V or 3V3) alone or both at the same time would affect the level of output. 5V changes to 4.5 V and 3V3 changes to 3V.

I would like to ask if there are any explanations for these problems and how I can resolve them.

Thank you and regards,

Hamid