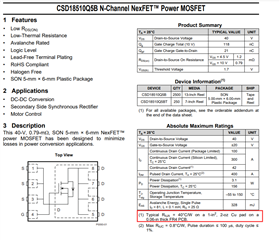

Other Parts Discussed in Thread: LM74700-Q1, , CSD18510Q5B, CSD18540Q5B, CSD19536KTT, CSD88584Q5DC

Hi, Support Team.

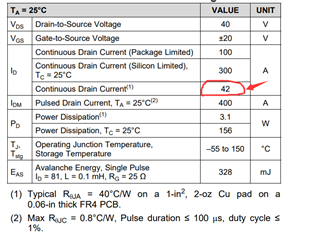

I plan to use two LM74700-Q1 to achieve ORING function, the input power is DC 18V~32V, the regular voltage is DC 24V, the current is 200A. does TI have a manual about the field tube selection method for using MOS tubes in parallel under high current? For example, if the voltage is 24V DC, the current is 200A, and the operating temperature is -40℃~85℃, how many can be driven by LM74700-Q1 to achieve the demand?

How many parallel connections should be used for the CSD19533Q5A for example?