Hey!

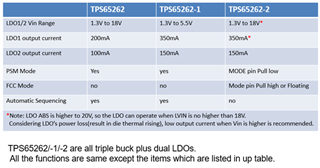

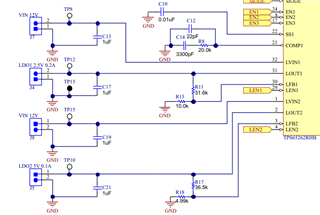

Two quick questions about the LDOs in the TPS65262. We are looking to use two TPS65262, and the LDOs do not provide quite enough power. Looking for 250mA, where the LDO max is 200mA. Our idea is to connect the inputs of two LDOs and connect the outputs of two LDOs.

My questions are:

1) Could we connect the inputs of two LDOs and the outputs of two LDOs? (Either on same TPS65262 chip or different chips, doesn't matter to us. Whichever you recommend)

2) What is the behavior of the LDO when Vout is set to 5V and the LDO input voltage is lower than output voltage? Will it passthrough? Passthrough is ideal, I want to make sure there is no under voltage lockout or anything of that sort specific to the LDOs

(Another note, I looked at the -1 and -2 versions which have the larger LDO output current limits but one version doesn't have automatic sequencing, and the other version has too narrow a LDO vin (5.5Vmax))