Hi TI Staff,

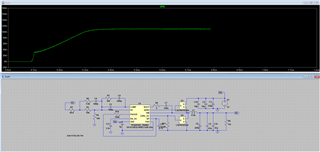

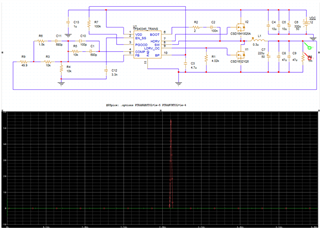

I simulated the eval board in both LTSpice and PSpice for TI, while output voltage matches with the description of the eval board, but the short circuit current limit was different. Here are screen shots for both simulation tool:

LTspice indicated short circuit current limit kicks in close to 120A, where PSpice for TI shows a 60A spike. The datasheet suggested 20A as the short circuit limit, which I have verified on the eval board. The question is that what I can do to improve the simulation and how do I adjust the short circuit limit? The datasheet shows calculation for R11, which affects the short-circuit limit, however I cannot find that part on the schematic nor on the PCB board.

Thanks,

Dave