Other Parts Discussed in Thread: LP5907, TPS7A21-Q1,

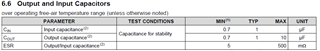

LP5907 Q1 has max output cap limitation of 10uF. is it allowed if i have high value of capacitor spread at longer distance from LDO output?

is there any guideliens regarding the 10uF value at what max distance i have to keep?

is it ok if i keep 10uF near LDO output and higher value at far distance?