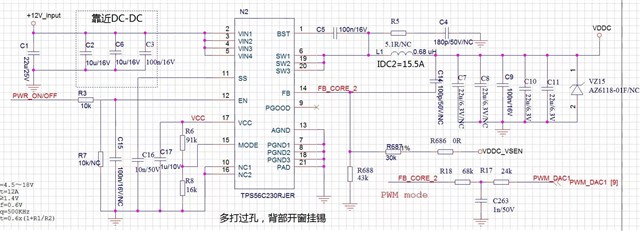

Other Parts Discussed in Thread: TPS563203

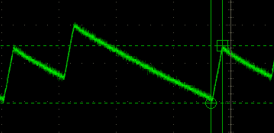

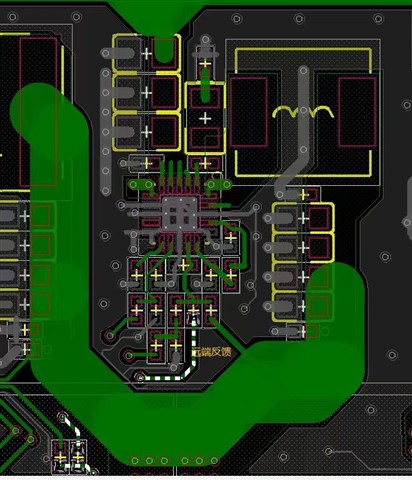

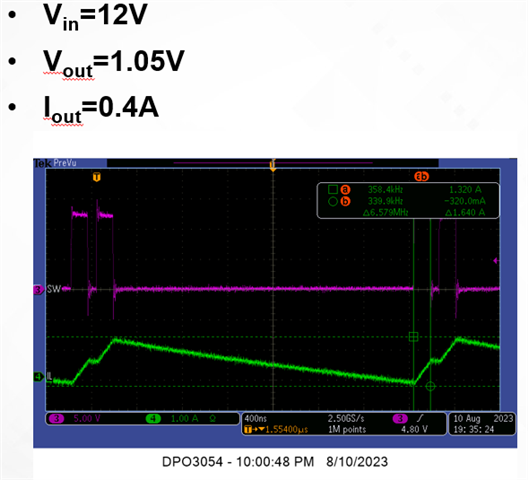

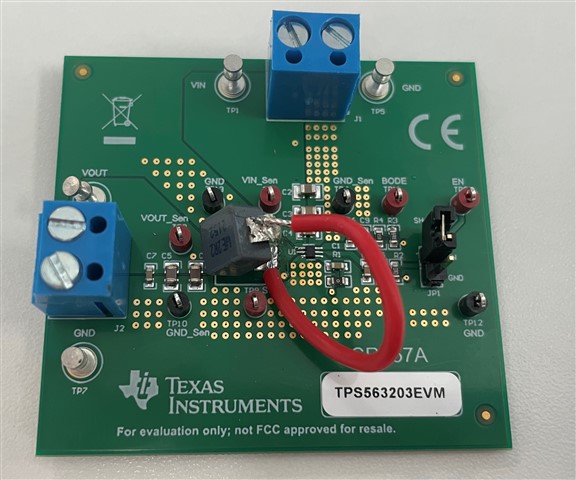

When I use this chip for remote feedback, a double pulse phenomenon will occur. As shown in the figure, the inductor current will be charged twice, but this will not happen for the near-end feedback. Can you tell me why?