Other Parts Discussed in Thread: UCC21551

Hi,

Regarding the following issues encountered during the open loop verification of UCC21551 driver chip, please help to resolve them.

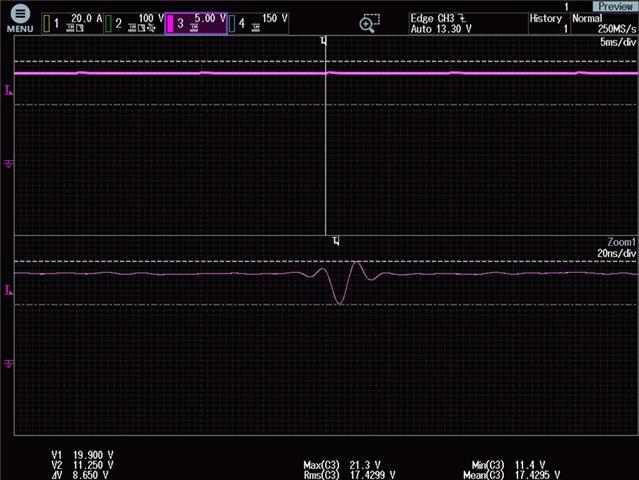

Problem 1: There may be spikes in the OUTA/OUTB pin drive pulse, especially when it is turned off. The downward spike is very large and lasts for about 5ns. The specification states that it is within 200ns, and -2V is allowed. Can you help confirm if there is a risk of -5.85V if this time is very short? What is the evaluation standard at this time?

Problem 2: At the time of the drive shutdown, there is a fluctuation in the voltage of VDD-VSS, with the minimum value reaching 11.25. If the time is ns, please help confirm if there is any risk. What are the evaluation criteria?

Problem 3: When the drive is turned off, there is a large current spike on the VSS, with a peak value of approximately 300mA. Please help confirm what the internal circuit logic diagram of the chip driver pin is and how the current spike is formed?

Best regards,

Zhixia Bai