Other Parts Discussed in Thread: LMG1210, LMG1205, LM5113, LM5114

Hello, TI experts,

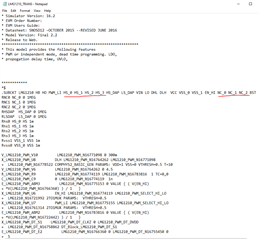

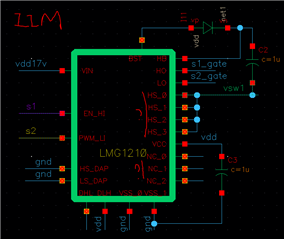

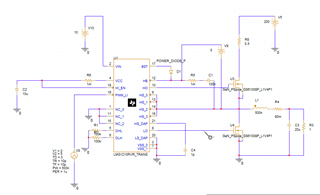

I tried to simulate a power converter circuit with real TI LMG1210 gate driver pspice model in cadence virtuoso environment.

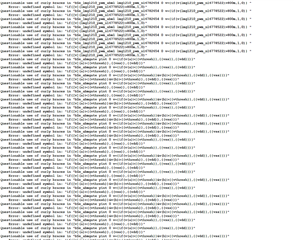

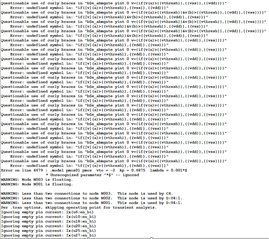

Saw this error when I imported it in as spice model.

I also tried with LMG1205, still not luck. But, I remember the LM5113 and LM5114 pspice model works before in cadence, and also remembered all the models works with LTSPICE. Attached the models (neither of them works).

Could you guide me how to fix the model that it will work with cadence tools?

Thanks,