Other Parts Discussed in Thread: TL431, UCC28064A, UCC28050, UCC2818, UCC28056, UCC28065, UCC28070A

Hi ,

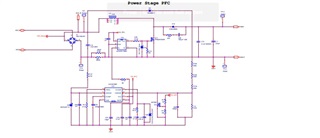

I have implemened 1kW PFC stage as AC to DC with PFC Operation and its working good.

in my output 100HZ ripple component comes as 5 to 15V.

Kinldy help,me to get rid of this 100HZ component traveling through output,do i need to adjust voltage loop?

advice me what to change?

Thankyou,

venkatesh