Hello TIer,

I have question about UCC5870-Q1 DESAT waveform in datasheet.

Why the VDESAT signal has twice ramp when VGE turned on? Could you help explain as detail? Thank you.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello TIer,

I have question about UCC5870-Q1 DESAT waveform in datasheet.

Why the VDESAT signal has twice ramp when VGE turned on? Could you help explain as detail? Thank you.

Hello Wenyung,

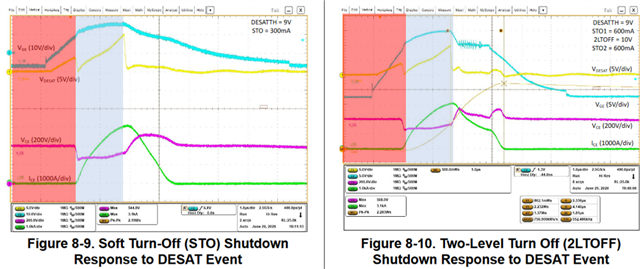

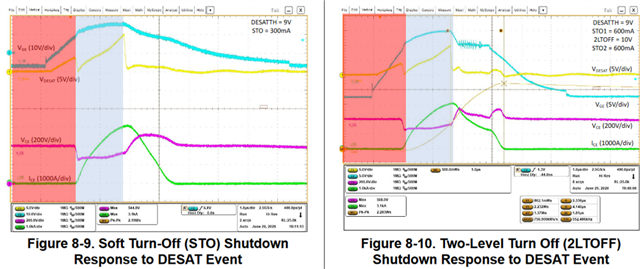

As Vge increases, Vce decreases. This Vce dv/dt can be coupled through the junction capacitance of the high voltage diode, causing a DESAT pin voltage drop. If you look at the waveforms, you can see that the Vce drop in the waveforms happen at around the same time of DESAT voltage drop.

We recommend using high voltage DESAT diode with minimal junction capacitance in your design to minimize the effect of Vce dv/dt on the DESAT voltage.

Hope that helps!

Vivian

Hi Wenyung,

SiC MOSFET will also have similar behavior. Actually, because SiC FETs usually have high turn-on speed and are usually used with smaller gate resistance, the dv/dt experienced by SiC FETs will usually be higher than that of IGBTs. Thus, a small junction capacitance high voltage diode becomes more crucial when designing the DESAT circuitry with SiC FETs.

Hope this helps!

Vivian