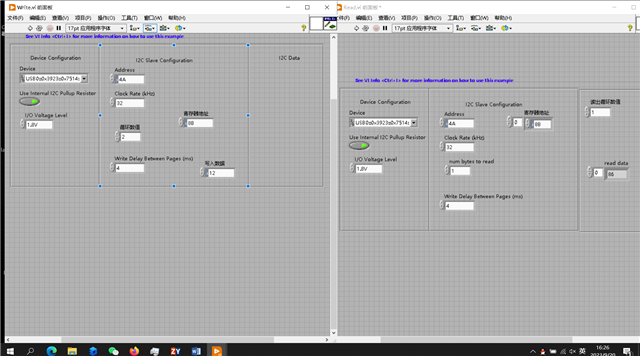

write:

read:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello liguidong,

we do not focus on this part, but in order to better help you please provide your schematics regarding this part.

Hi,Nicholas,

My detailed question is shown below.

I want to give VPLL1_ The TYPE register writes a data 0x12 with device address 0x4A and register address 0x4A. When I was writing and reading data, I used an oscilloscope to capture the timing chart of writing and reading.

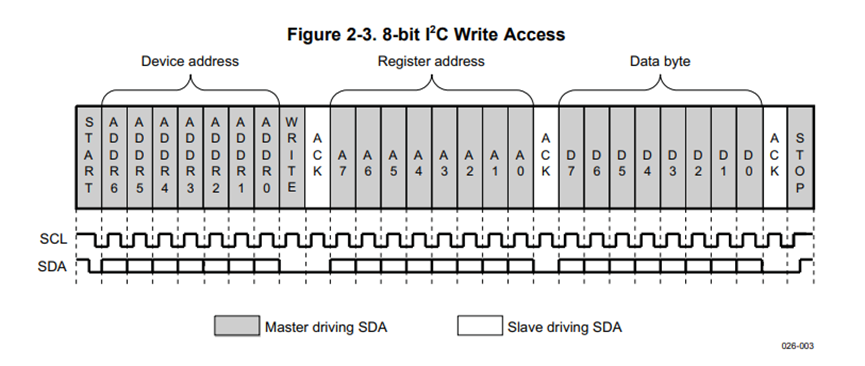

This is a schematic diagram of the standard IIC writing timing:

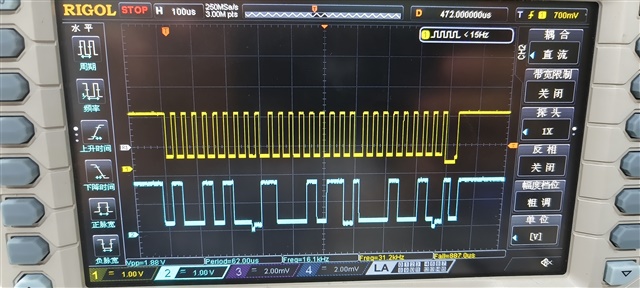

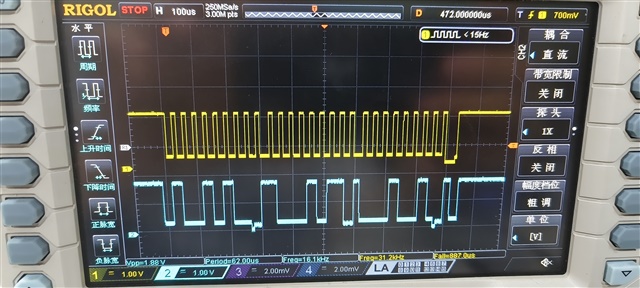

This is the IIC write timing chart I captured using an oscilloscope:

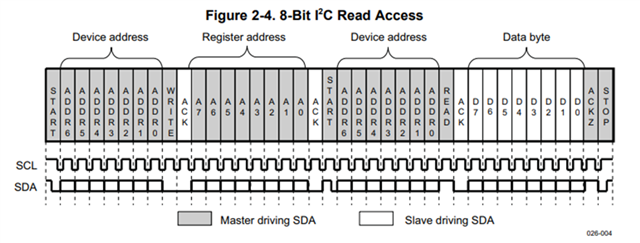

This is a schematic diagram of the standard IIC reading timing:

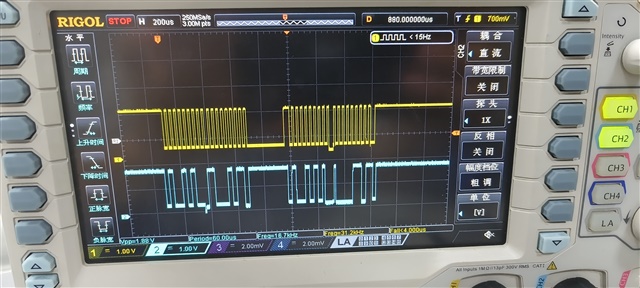

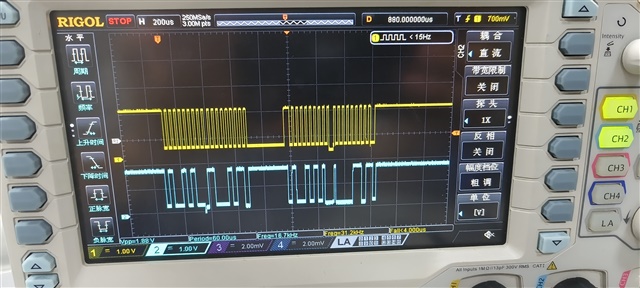

This is the IIC reading timing chart I captured using an oscilloscope:

The timing charts for writing and reading data meet the standard IIC timing chart requirements, but there is a discrepancy between the data I wrote and the data I read. So could you please help me answer the possible reason for the inconsistent data read and written during IIC communication?

Regards,

Liguidong

Liguidong,

this device has two I2C lines, it's why I'm asking to see the schematic with all of the pins on this, I need to know that you're writing to the correct lines.

But the first thing to look at would be the speeds, in the screen shot for writing it looks like you're driving the clock speed to be 32kHz, this isn't one of the three accepted speeds of 100kHz, 400kHz, & 3.4MHz, which corresponds to the kbps & Mpbs, respectively. Try changing that first.

BR,

Nicholas