Hi team,

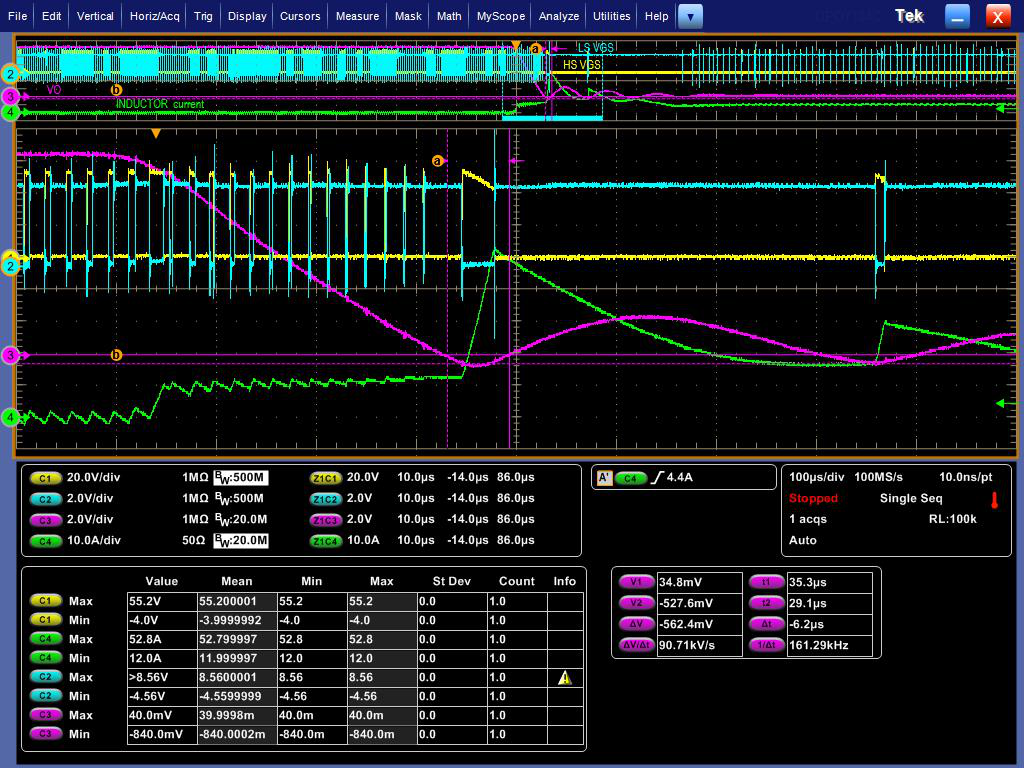

My customer is using our LM25149-Q1EVM and do the short circuit protection test by the e-load.

for the delay time of ISNS+ is about 65ns, the current limit threshold is 60mV and we use 30V as input,

the IL peak would be 14.86A as the calculation.

how to determine the Io peak is reasonable and suitable or not?

We measured the output current peak would increase to 48A, and the peak occur at 150ms after the short occurred.

Is the spike current caused by the power from output cap?

Thanks,

Gilbert.