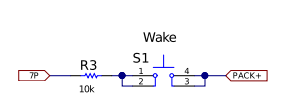

I have a design that follows the circuitry of the evaluation board, an exception being that my design does not have a switch S1 that can tie the 7P net to the PACK+ net to Wake up the chip.

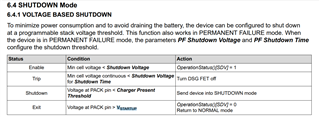

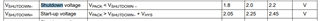

In testing, we have seen that the SMBus communication only works if the PACK pin 25 is high. In other words, if the CHG/DSG FETs are off, then we cannot communicate with the chip via SMBus. We believe the chip is in shutdown mode. While still testing, we are working around this by turning on the CHG/DSG FETs to get the PACK pin high.

I have several questions regarding this topic:

1. Can we communicate to the device via SMBus when the chip is in shutdown mode?

2. Is there a way to wake up the chip from shutdown without the use of the PACK pin 25 on the chip?

3. What is the proper implementation for this chip in a product? Does it require the use of a button or controller signal to pass 7P to PACK+ to wake up the chip in order to communicate with it via SMBus?

4. When the device is in shutdown mode, are any fuel gauge measurements being taken or is the chip completely off?

5. Will SMBus communication only be operable while the PACK pin is high, or will a high pulse on the PACK pin wake up the chip and keep communications operable even after the pulse ends?