Hello:

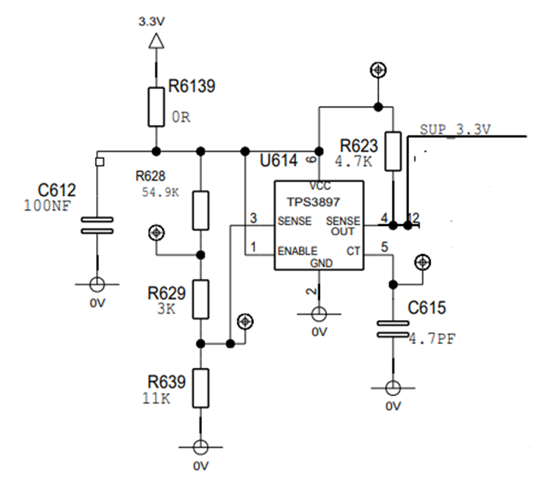

Schematic is the following:

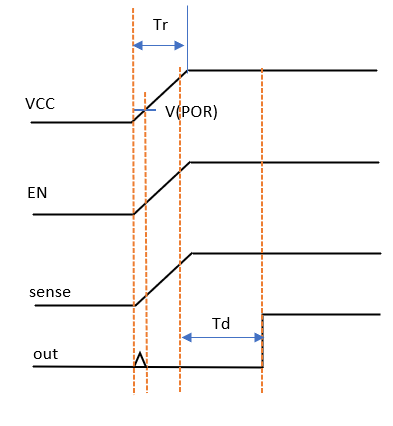

Timming is the fillowing:

My question is the following:

1. Whether output waveform will link with VCC ramp up Tr or not? If the ramp out is very fast, for example VCC going to 3.3V within 20us, what will happen?

2. When 0<Vcc<V(POR), equal to the VCC because of pull-up R623

3. When Vcc=V(POR), whether out goes to low immediately or need to delay a short time? Whether statup delay need to consider this time slot or not?

4. When Vcc>VCC threshold, out goes to high with Td. Because of power on progress, the Td=startup dealy (50us)+ tpd (r)?

Thanks a lot~