Hi team,

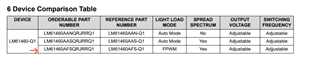

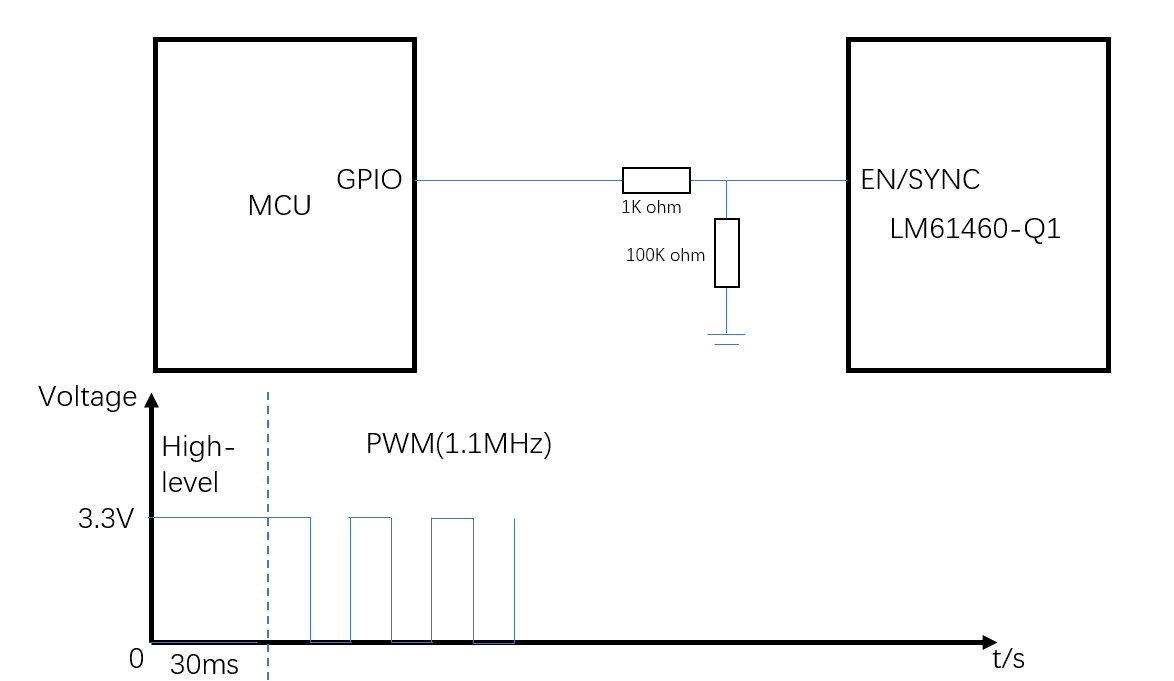

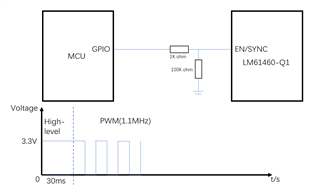

My customer do not want to use PFM mode in light load, they want to use FPWM. So they input PWM waveform at EN/SYNC pin when in light load.

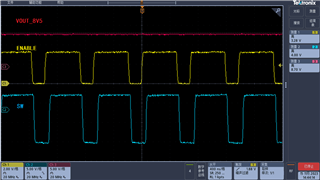

They worry that this will cause abnormal situation, so they set the EN pin to high level for 30ms, then they change it to PWM. Is it ok?

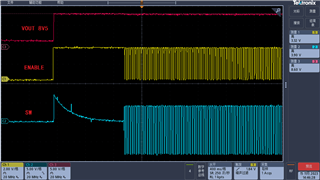

I put the real waveform below. Pls have a check.

VIN =12V VOUT =8.5V IOUT=50mA

Regards,

Peter