Hi team,

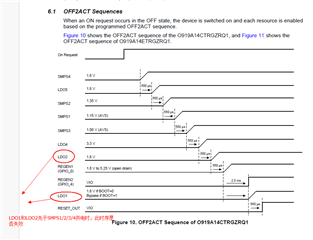

Here is my customer device solution background: The platform is TDA2EGBHQCBDQ1, and the PMIC is O919A14CTRGZRQ1 (TPS65919).

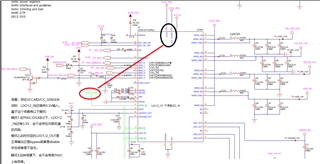

There is a scene during operation: When the PMIC's VCCA and VCC_SENSE are turning off and the voltage is 0V, but LDO12_IN still maintains 3.3V input.

Based on this scene, the customer have the following questions,

Question 1: What will happen when LDO12_IN is supplied before SMPS1/2/3 power up?

Question 2: In this scene, is there any risk of backward current inside the PMIC?

Question 3: They wonder whether LDO1/2 can output normally at this time, or disable and no output?

Question 4: In this scene, will it cause PMIC power up abnormally?

Here is their schematic:

Question 5: If the LDO1/2 can output normally, what will change for the power-on sequence?

Looking forward to your reply, thanks in advance!

Best Regards!

Jack