Hi team,

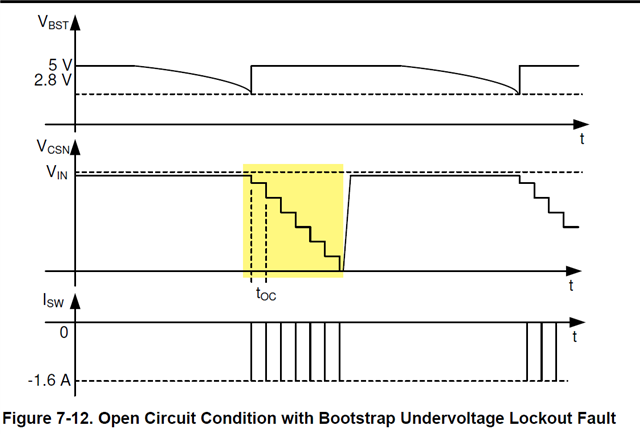

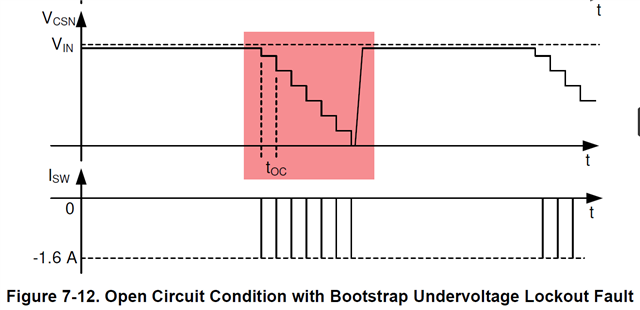

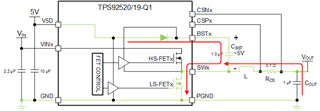

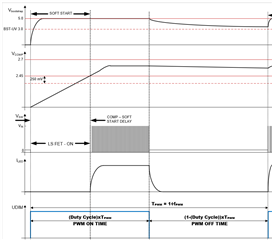

Could you please help me understand why operating at higher input voltage, the bootstrap voltage would drop below UVLO?

And Why after high-side current limit is triggered and then the low-side current limit is triggered?

Why the output voltage drops as below?