Hello, expert at TI!

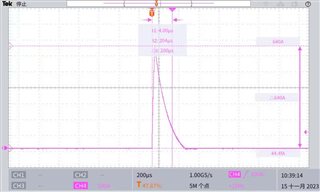

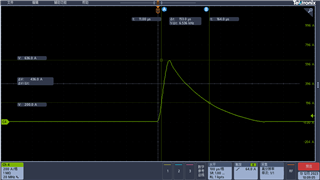

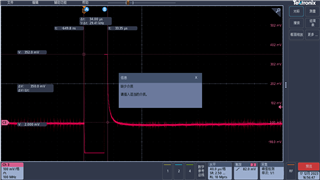

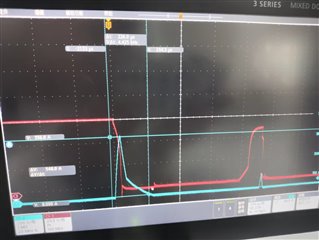

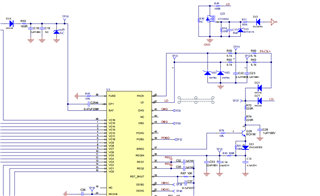

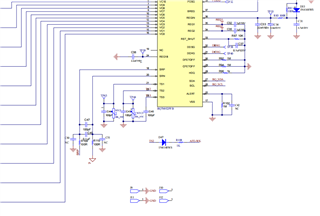

When I use bq76952, when my OCD1 delay is set to 300ms, that is, the value written by the register is 0x58, but the OCD1 delay waveform captured by the oscilloscope displays the actual time of 430ms. Other fault delay times are normal, such as OCD2, may I ask what causes this?

thanks.