Hi Team,

I would like to ask a question: what is the mask registers?

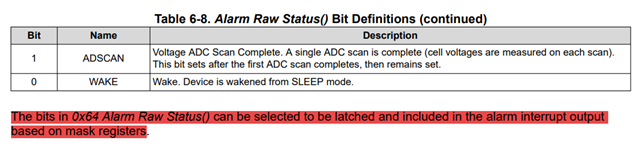

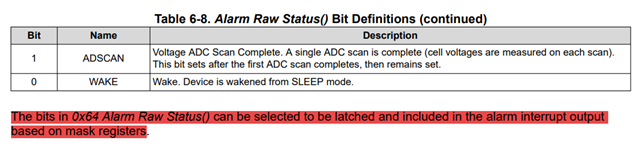

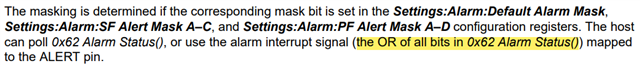

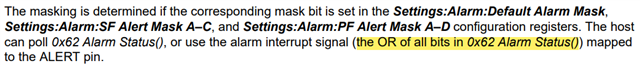

I am confused about the following words:

Thanks a lot.

BRs,

Francis

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

I would like to ask a question: what is the mask registers?

I am confused about the following words:

Thanks a lot.

BRs,

Francis

Hi Francis,

Each bit in Alarm Raw Status can be selected whether it will be latched into Alarm Status when it asserts. How the part knows which bits to latch is determined by the alarm mask. When the part first powers up, it loads a mask register from Data Memory (Default Alarm Mask). These bits can also be modified during operation without needing to change the Data Memory value by using the Alarm Enable command. For example, if Default Alarm Mask was 0x0000, then no bit in Alarm Raw Status would be latched into Alarm Status if they asserted. Then, for example, if you want the ALERT to assert whenever the FULLSCAN bit in Alarm Raw Status asserts, you can write to set the FULLSCAN bit in Alarm Enable. Then after this, if the FULLSCAN bit asserts in Alarm Raw Status, it will be latched into the FULLSCAN bit in Alarm Status, and the ALERT pin will be asserted. You can then clear the latched bit by writing a 1 to the FULLSCAN bit in Alarm Status.

Thanks,

Terry

Hi Terry,

Thanks a lot! So clear that I totally understand the relationship between Alarm Raw Status and Alarm Status. I would like to ask you some further questions, thanks in advance:

Thanks again!

BRs,

Francis

Hi Francis, I'll address each question below:

Thanks,

Terry