Other Parts Discussed in Thread: MSPM0L1306

I am trying to implement a very simple state machine.

- When enable rises it should execute a power up sequence.

- When enable falls or the input power falls it should execute a power down sequence.

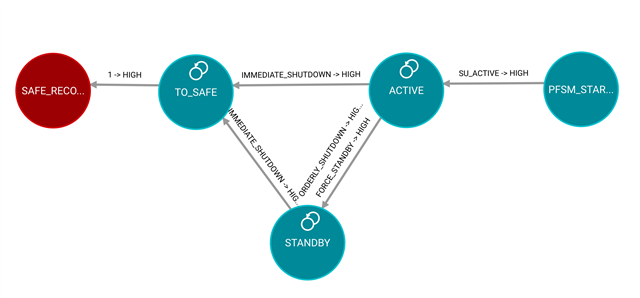

(It flows right to left so the trigger indications can be right side up.

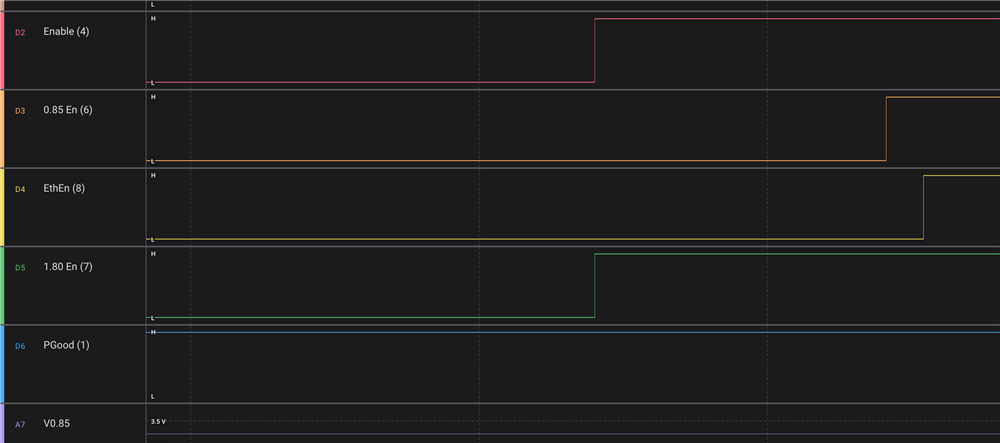

The power up when ENABLE goes high seems to work fine. This shows red ENABLE signal starting the sequence to drive 3 GPO outputs. I am not enabling the bucks yet, just trying to test the state machine functionality before implementing the full sequence.

It will also power down when ENABLE falls.

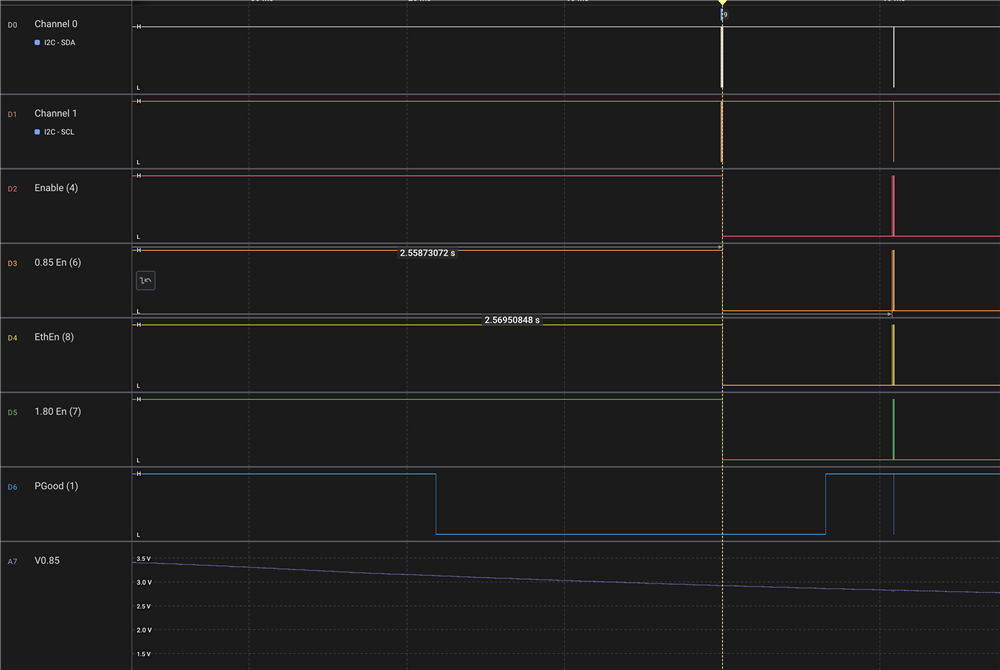

I can't get it to begin a power down when VCCA < VCCA UV. Here is a logic analyzer trace showing the power fail process.

The bottom trace in purple is the VCCA. You can see it falling from 3.3V.

The Blue trace is PGOOD. You can see PGOOD drop as expected. Unfortunately the GPIO sequence does not start after PGOOD falls. The are eventually cleared by I2C commands from a processor that also detected the power failure. Since they all drop at the same time, I can tell that the PFSM sequence was not activated. ENABLE is also drive low by the processor when it detects low input power.

I have VCCA_GRP_SEL set to "OTHER rail group". VCCA_VMON_EN = Enabled OV and UV.

I have OTHER_RAIL_TRIG set to "Orderly Shutdown"

You can see from the state machine diagram I am trying to move from Active to Standby on Orderly Shutdown = High.

Can you advise what I am missing?

I would like the state machine to work because it can identify the power failure earlier and start the power down process more reliably. Also, I just want to make sure I understand the state machine development process. There are additional features we would like to add, but it seems sensible to make the easiest case possible work first.

I tried to attach the Scaleable PMICs GUI design files below. Seems like I had to add a .txt extension to allow them to load here.

It would really be nice if you could provide a complete simple state machine as a template. The existing simple template lacks all the implementation details. I could not get it to work at all, so I scaled back to this model.

CUSTOMER_NVM_ID=0xb5 VMON_DEGLITCH_SEL=0x0 VCCA_VMON_EN=0x1 VMON1_EN=0x0 VMON2_EN=0x0 VCCA_OV_THR=0x3 VCCA_UV_THR=0x3 VCCA_PG_SET=0x0 VCCA_GRP_SEL=0x3 LPM_EN_DISABLES_VCCA_VMON=0x0 MP_CONFIG=0x2 BUCK1_EN=0x0 BUCK1_FPWM=0x0 BUCK1_FPWM_MP=0x0 BUCK1_VMON_EN=0x0 BUCK1_VSEL=0x0 BUCK1_PLDN=0x1 BUCK1_RV_SEL=0x0 BUCK1_SLEW_RATE=0x2 BUCK1_ILIM=0x7 BUCK1_VSET1=0x41 BUCK1_VSET2=0x2d BUCK1_OV_THR=0x2 BUCK1_UV_THR=0x2 BUCK1_GRP_SEL=0x1 BUCK1_RESET=0x0 BUCK1_FREQ_SEL=0x0 BUCK1_SEL_NEG_OCP_HYST=0x0 BUCK1_SEL_POS_OCP_HYST=0x1 BUCK1_SEL_ISENSE_SLOPE_COMPENSATION=0x2 BUCK1_SEL_VOUT_ADC_LEVEL=0x0 BUCK1_SEL_PHASE_SHEDD=0x0 BUCK1_SEL_PHASE_ADD=0x1 EN_LOAD_COMP_BLANK=0x1 BUCK1_SEL_OUTPUT_CAPS=0x2 BUCK1_SEL_RAMP=0x2 BUCK1_EN_P_10M_BODY_DIODE=0x1 BUCK1_DOUBLE_PFM_PULSE=0x0 BUCK1_CHANGE_2MHZ_BELOW_0V5=0x0 BUCK1_EN_RADAR_MODE=0x0 BUCK1_SEL_FB_FILTER=0x3 swc_buck_hiz_1=0x0 BUCK2_EN=0x0 BUCK2_FPWM=0x0 BUCK2_VMON_EN=0x0 BUCK2_VSEL=0x0 BUCK2_PLDN=0x1 BUCK2_RV_SEL=0x0 BUCK2_SLEW_RATE=0x2 BUCK2_ILIM=0x7 BUCK2_VSET1=0x41 BUCK2_VSET2=0x2d BUCK2_OV_THR=0x2 BUCK2_UV_THR=0x2 BUCK2_GRP_SEL=0x1 BUCK2_RESET=0x0 BUCK2_FREQ_SEL=0x0 BUCK2_SEL_NEG_OCP_HYST=0x0 BUCK2_SEL_POS_OCP_HYST=0x1 BUCK2_SEL_ISENSE_SLOPE_COMPENSATION=0x2 BUCK2_SEL_VOUT_ADC_LEVEL=0x0 BUCK2_SEL_OUTPUT_CAPS=0x2 BUCK2_SEL_RAMP=0x2 BUCK2_EN_P_10M_BODY_DIODE=0x1 BUCK2_DOUBLE_PFM_PULSE=0x0 BUCK2_CHANGE_2MHZ_BELOW_0V5=0x0 BUCK2_EN_RADAR_MODE=0x0 BUCK2_SEL_FB_FILTER=0x3 swc_buck_hiz_2=0x0 BUCK3_EN=0x0 BUCK3_FPWM=0x0 BUCK3_FPWM_MP=0x0 BUCK3_VMON_EN=0x0 BUCK3_VSEL=0x0 BUCK3_PLDN=0x1 BUCK3_RV_SEL=0x0 BUCK3_SLEW_RATE=0x2 BUCK3_ILIM=0x3 BUCK3_VSET1=0xb2 BUCK3_VSET2=0xb2 BUCK3_OV_THR=0x2 BUCK3_UV_THR=0x2 BUCK3_GRP_SEL=0x1 BUCK3_RESET=0x0 BUCK3_FREQ_SEL=0x0 BUCK3_SEL_NEG_OCP_HYST=0x0 BUCK3_SEL_POS_OCP_HYST=0x1 BUCK3_SEL_ISENSE_SLOPE_COMPENSATION=0x2 BUCK3_SEL_VOUT_ADC_LEVEL=0x0 BUCK3_SEL_PHASE_SHEDD=0x0 BUCK3_SEL_PHASE_ADD=0x1 BUCK3_SEL_OUTPUT_CAPS=0x2 BUCK3_SEL_RAMP=0x2 BUCK3_EN_P_10M_BODY_DIODE=0x1 BUCK3_DOUBLE_PFM_PULSE=0x0 BUCK3_CHANGE_2MHZ_BELOW_0V5=0x0 BUCK3_EN_RADAR_MODE=0x0 BUCK3_SEL_FB_FILTER=0x3 swc_buck_hiz_3=0x0 BUCK4_EN=0x0 BUCK4_FPWM=0x0 BUCK4_VMON_EN=0x0 BUCK4_VSEL=0x0 BUCK4_PLDN=0x1 BUCK4_RV_SEL=0x0 BUCK4_SLEW_RATE=0x2 BUCK4_ILIM=0x3 BUCK4_VSET1=0x73 BUCK4_VSET2=0x73 BUCK4_OV_THR=0x2 BUCK4_UV_THR=0x2 BUCK4_GRP_SEL=0x1 BUCK4_RESET=0x0 BUCK4_FREQ_SEL=0x0 BUCK4_SEL_NEG_OCP_HYST=0x0 BUCK4_SEL_POS_OCP_HYST=0x1 BUCK4_SEL_ISENSE_SLOPE_COMPENSATION=0x2 BUCK4_SEL_VOUT_ADC_LEVEL=0x0 BUCK4_SEL_OUTPUT_CAPS=0x2 BUCK4_SEL_RAMP=0x2 BUCK4_EN_P_10M_BODY_DIODE=0x1 BUCK4_DOUBLE_PFM_PULSE=0x0 BUCK4_CHANGE_2MHZ_BELOW_0V5=0x0 BUCK4_EN_RADAR_MODE=0x0 BUCK4_SEL_FB_FILTER=0x3 swc_buck_hiz_4=0x0 SEL_LOOP_NEG_HYST=0x2 SEL_GATE_EARLY_SENSE=0x0 SEL_TRAD_NON_OVERLAP=0x0 SEL_RAMP_ARTIF=0x1 EN_SW_RT_SHORT_DETECTORS=0x0 EN_IAVE_LOOP_INJECTOR=0x0 EN_PLL_PROP_EXTEND=0x1 EN_SMART_OCP_BLANK=0x1 SEL_HS_DETECTOR=0x1 EN_LONG_PFM_EXIT_CNTR=0x1 EN_NEG_OCP=0x1 EN_POS_OCP=0x1 EN_NEG_OCP_PREVENT_DAC_STEPPING=0x0 EN_POS_OCP_PREVENT_DAC_STEPPING=0x0 EN_PFM_LOAD=0x1 EN_DOT_MODE=0x1 LOOP_COEFF_I_BALANCE=0x1 SEL_ZERO_CROSS_FILTER_AVE=0x1 EN_AUTO_LOOP_COEFFS=0x1 LOOP_COEFF_FB_MSB=0x1 EN_LONG_ZERO_CROSS_FILTER=0x0 FORCE_SS_ADAPT=0x0 EN_SLOW_PLL_COEFFS=0x0 EN_PFM_PULSE_WAIT_LS_OCP=0x1 EN_SW_SHORT_DETECTORS=0x1 EN_FAST_PLL_0P7=0x1 EN_FAST_VOUT_INTEGRATION=0x1 EN_I_BALANCE_INTEGRATOR=0x1 DIS_PFM_WAITS_LS_DETECTOR=0x0 DIS_PFM_WAITS_HS_DETECTOR=0x0 DIS_DVS_WAIT_COMPARATORS=0x0 EN_CONSTANT_PLL_DVS_COEFF=0x0 EN_SLOW_PLL_0P3=0x1 EN_M_10M_TRAN_DETECTOR=0x1 EN_FAST_INTEGRATION_BYPASS_RAMP_RES=0x1 EN_LS_AFTER_HIZ=0x0 EN_PWM_LS_DETECTION=0x0 I_COEFF=0x1 BUCK_NEG_ILIM=0x1 EN_ADAPTIVE_SINGLE_SHOT=0x1 FIXED_SS_LENGTH=0x18 LONG_SINGLE_SHOT=0x0 BUCK1_MAX_ILIM=0x7 BUCK2_MAX_ILIM=0x7 BUCK3_MAX_ILIM=0x7 BUCK4_MAX_ILIM=0x7 GPIO1_OD=0x0 GPIO1_DIR=0x1 GPIO1_SEL=0x3 GPIO1_PU_SEL=0x0 GPIO1_PU_PD_EN=0x1 GPIO1_DEGLITCH_EN=0x0 GPIO1_OUT=0x0 GPIO2_OD=0x0 GPIO2_DIR=0x1 GPIO2_SEL=0x0 GPIO2_PU_SEL=0x0 GPIO2_PU_PD_EN=0x1 GPIO2_DEGLITCH_EN=0x0 GPIO2_OUT=0x0 GPIO3_OD=0x0 GPIO3_DIR=0x0 GPIO3_SEL=0x0 GPIO3_PU_SEL=0x1 GPIO3_PU_PD_EN=0x1 GPIO3_DEGLITCH_EN=0x0 GPIO3_OUT=0x0 GPIO4_OD=0x0 GPIO4_DIR=0x0 GPIO4_SEL=0x1 GPIO4_PU_SEL=0x0 GPIO4_PU_PD_EN=0x1 GPIO4_DEGLITCH_EN=0x1 GPIO4_OUT=0x0 ENABLE_POL=0x0 GPIO5_OD=0x0 GPIO5_DIR=0x0 GPIO5_SEL=0x0 GPIO5_PU_SEL=0x0 GPIO5_PU_PD_EN=0x1 GPIO5_DEGLITCH_EN=0x0 GPIO5_OUT=0x0 GPIO6_OD=0x0 GPIO6_DIR=0x1 GPIO6_SEL=0x0 GPIO6_PU_SEL=0x0 GPIO6_PU_PD_EN=0x1 GPIO6_DEGLITCH_EN=0x0 GPIO6_OUT=0x0 GPIO7_OD=0x0 GPIO7_DIR=0x1 GPIO7_SEL=0x0 GPIO7_PU_SEL=0x0 GPIO7_PU_PD_EN=0x1 GPIO7_DEGLITCH_EN=0x0 GPIO7_OUT=0x0 VMON1_RV_SEL=0x0 VMON1_OV_THR=0x0 VMON1_UV_THR=0x0 VMON1_RANGE=0x0 VMON1_PG_SET=0x0 VMON1_SLEW_RATE=0x0 VMON1_GRP_SEL=0x0 GPIO8_OD=0x0 GPIO8_DIR=0x1 GPIO8_SEL=0x0 GPIO8_PU_SEL=0x0 GPIO8_PU_PD_EN=0x1 GPIO8_DEGLITCH_EN=0x0 GPIO8_OUT=0x0 VMON2_RV_SEL=0x0 VMON2_OV_THR=0x0 VMON2_UV_THR=0x0 VMON2_RANGE=0x0 VMON2_PG_SET=0x0 VMON2_SLEW_RATE=0x0 VMON2_GRP_SEL=0x0 GPIO9_OD=0x0 GPIO9_DIR=0x0 GPIO9_SEL=0x0 GPIO9_PU_SEL=0x1 GPIO9_PU_PD_EN=0x1 GPIO9_DEGLITCH_EN=0x0 GPIO9_OUT=0x0 GPIO10_OD=0x0 GPIO10_DIR=0x1 GPIO10_SEL=0x0 GPIO10_PU_SEL=0x0 GPIO10_PU_PD_EN=0x0 GPIO10_DEGLITCH_EN=0x0 GPIO10_OUT=0x0 I2C_SPI_SEL=0x0 I2C1_SPI_CRC_EN=0x0 I2C2_CRC_EN=0x0 I2C1_ID=0x48 I2C2_ID=0x12 SPMI_CRC_EN=0x1 SPMI_MASTER_SEL=0x1 SPMI_CLK_SEL=0x2 SPMI_SLAVE_PASSIVE=0x0 SPMI_IF_SEL=0x0 SPMI_RETRY_LIMIT=0x3 SPMI_SLAVE_ASR_HOLD=0x0 SPMI_WD_AUTO_BOOT=0x1 SPMI_EN=0x0 SPMI_WD_EN=0x0 SPMI_WAKEUP_EN=0x0 SPMI_WD_BOOT_INTERVAL=0x8 SPMI_WD_RUNTIME_INTERVAL=0x8 SPMI_WD_RESPONSE_TIMEOUT=0x8 SPMI_PFSM_RESPONSE_TIMEOUT=0x8 SPMI_WD_BOOT_BIST_TIMEOUT=0x8 SPMI_WD_RUNTIME_BIST_TIMEOUT=0x8 BOOT_DELAY=0x0 SPMI_SID=0x5 SPMI_MID=0x0 SPMI_SLAVE_CNT=0x1 FORCE_CLK_GATE=0x0 INT_LDO_PD_FORCE=0x0 MCU_RAIL_TRIG=0x1 SOC_RAIL_TRIG=0x1 OTHER_RAIL_TRIG=0x1 SEVERE_ERR_TRIG=0x0 MODERATE_ERR_TRIG=0x1 GPIO1_FSM_MASK=0x1 GPIO1_FSM_MASK_POL=0x0 GPIO2_FSM_MASK=0x1 GPIO2_FSM_MASK_POL=0x0 GPIO3_FSM_MASK=0x1 GPIO3_FSM_MASK_POL=0x0 GPIO4_FSM_MASK=0x1 GPIO4_FSM_MASK_POL=0x0 GPIO5_FSM_MASK=0x1 GPIO5_FSM_MASK_POL=0x0 GPIO6_FSM_MASK=0x1 GPIO6_FSM_MASK_POL=0x0 GPIO7_FSM_MASK=0x1 GPIO7_FSM_MASK_POL=0x0 GPIO8_FSM_MASK=0x1 GPIO8_FSM_MASK_POL=0x0 GPIO9_FSM_MASK=0x1 GPIO9_FSM_MASK_POL=0x0 GPIO10_FSM_MASK=0x1 GPIO10_FSM_MASK_POL=0x0 GPIO1_FALL_MASK=0x1 GPIO2_FALL_MASK=0x1 GPIO3_FALL_MASK=0x1 GPIO4_FALL_MASK=0x1 GPIO5_FALL_MASK=0x1 GPIO6_FALL_MASK=0x1 GPIO7_FALL_MASK=0x1 GPIO8_FALL_MASK=0x1 GPIO1_RISE_MASK=0x1 GPIO2_RISE_MASK=0x1 GPIO3_RISE_MASK=0x1 GPIO4_RISE_MASK=0x1 GPIO5_RISE_MASK=0x1 GPIO6_RISE_MASK=0x1 GPIO7_RISE_MASK=0x1 GPIO8_RISE_MASK=0x1 GPIO9_FALL_MASK=0x1 GPIO9_RISE_MASK=0x1 GPIO10_FALL_MASK=0x1 GPIO10_RISE_MASK=0x1 BUCK1_ILIM_MASK=0x0 BUCK1_OV_MASK=0x0 BUCK1_UV_MASK=0x0 BUCK2_ILIM_MASK=0x0 BUCK2_OV_MASK=0x0 BUCK2_UV_MASK=0x0 BUCK3_ILIM_MASK=0x0 BUCK3_OV_MASK=0x0 BUCK3_UV_MASK=0x0 BUCK4_OV_MASK=0x0 BUCK4_UV_MASK=0x0 BUCK4_ILIM_MASK=0x0 VCCA_OV_MASK=0x0 VCCA_UV_MASK=0x0 SOFT_REBOOT_MASK=0x0 ENABLE_MASK=0x0 FSD_MASK=0x1 TWARN_MASK=0x0 BIST_PASS_MASK=0x1 EXT_CLK_MASK=0x1 BIST_FAIL_MASK=0x1 REG_CRC_ERR_MASK=0x1 SPMI_ERR_MASK=0x1 NINT_READBACK_MASK=0x1 NRSTOUT_READBACK_MASK=0x1 IMM_SHUTDOWN_MASK=0x0 MCU_PWR_ERR_MASK=0x1 SOC_PWR_ERR_MASK=0x1 ORD_SHUTDOWN_MASK=0x1 WD_MASK=0x1 COMM_FRM_ERR_MASK=0x1 COMM_CRC_ERR_MASK=0x1 COMM_ADR_ERR_MASK=0x1 I2C2_CRC_ERR_MASK=0x1 I2C2_ADR_ERR_MASK=0x1 EN_DRV_READBACK_MASK=0x1 NRSTOUT_SOC_READBACK_MASK=0x1 ESM_MCU_PIN_MASK=0x1 ESM_MCU_RST_MASK=0x1 ESM_MCU_FAIL_MASK=0x1 VMON1_OV_MASK=0x1 VMON1_UV_MASK=0x1 VMON2_OV_MASK=0x1 VMON2_UV_MASK=0x1 PGOOD_SEL_BUCK1=0x2 PGOOD_SEL_BUCK2=0x0 PGOOD_SEL_BUCK3=0x2 PGOOD_SEL_BUCK4=0x2 PGOOD_SEL_VCCA=0x1 PGOOD_SEL_TDIE_WARN=0x1 PGOOD_SEL_NRSTOUT=0x0 PGOOD_SEL_NRSTOUT_SOC=0x0 PGOOD_POL=0x0 PGOOD_WINDOW=0x1 PGOOD_SEL_VMON1=0x0 PGOOD_SEL_VMON2=0x0 SS_EN=0x0 SS_DEPTH=0x0 SS_MODE=0x1 SS_PARAM1=0x7 SS_PARAM2=0xc STARTUP_DEST=0x3 LP_STANDBY_SEL=0x0 PFSM_DELAY1=0x10 PFSM_DELAY2=0x20 PFSM_DELAY3=0x40 PFSM_DELAY4=0x80 EXT_CLK_FREQ=0x0 TWARN_LEVEL=0x0 I2C1_HS=0x0 I2C2_HS=0x0 EN_ILIM_FSM_CTRL=0x1 NSLEEP1_MASK=0x1 NSLEEP2_MASK=0x1 TSD_ORD_LEVEL=0x0 PFSM_DELAY_STEP=0x10 USER_SPARE_1=0x0 USER_SPARE_2=0x0 USER_SPARE_3=0x0 USER_SPARE_4=0x0 refsys_bg_buf_hi_bw=0x0 refsys_sel_ibias=0x0 safety_speedup=0x1 safety_sel_ibias=0x0 safety_bg_buf_hi_bw=0x0 EN_OVP=0x1 DIS_UVLO_OVP_RESET=0x0 DIS_TSD=0x0 VSYS_DEAD_LOCK_EN=0x0 PFSM_ERR_RESET_DIS=0x0 ABIST_ERROR_MASK=0x0 DIS_NRSTOUT_MCU_I2C_SPI_RESET=0x0 SLOW_AUTOZERO_SEL=0x0 EN_FIXED_DPLL_FREQ=0x0 SEL_RC_OSC=0x0 DISABLE_VM_NARROW_LIMITS=0x0 DISABLE_CHANGE_BG=0x0 DISABLE_USE_TRIMS=0x0 WD_EN_EE=0x1 PFSM_SEQ_MIN_TIME=0x1 SRAM_RELOAD_LIMIT=0x2 PFSM_PROXY_BRANCH_DIS=0x0 FREQ_SEL_UNLOCK=0x0 REG_CRC_EN=0x0 EN_INITIALIZE_DPLL_RESTART=0x0 PFSM_ERR_MASK=0x0 CLKMON_ERR_MASK=0x0 DIS_REFSYS_UVLO_OVP_RESET=0x0 BACKWARD_COMPATIBLE=0x0 WD_RST_EN=0x1 WD_FAIL_TH=0x7 WD_RST_TH=0x7 FAST_BOOT_BIST=0x1 VMON_ABIST_EN=0x0 WD_EN=0x0 WD_LONGWIN=0x0 FAST_BIST=0x1 ESM_MCU_EN=0x0 RECOV_CNT_THR=0x0 ; instruction_set_version 2 ; enable_optimization true pfsm_start: TRIG_SET DEST=SAFE_RECOVERY ID=0 SEL=1 TYPE=HIGH IMM=1 EXT=1 TRIG_SET DEST=2Safe ID=1 SEL=IMMEDIATE_SHUTDOWN TYPE=HIGH IMM=1 EXT=0 TRIG_SET DEST=2Safe ID=2 SEL=IMMEDIATE_SHUTDOWN TYPE=HIGH IMM=1 EXT=0 TRIG_SET DEST=2STANDBY ID=3 SEL=ORDERLY_SHUTDOWN TYPE=HIGH IMM=1 EXT=0 TRIG_SET DEST=2STANDBY ID=4 SEL=FORCE_STANDBY TYPE=HIGH IMM=1 EXT=0 TRIG_SET DEST=2active ID=5 SEL=SU_ACTIVE TYPE=HIGH IMM=0 EXT=0 TRIG_MASK 0xFFFFFDF END 2active: REG_WRITE_MASK_IMM ADDR=0x82 DATA=0x00 MASK=0xEF REG_WRITE_MASK_IMM ADDR=0x2B DATA=0x01 MASK=0xFE REG_WRITE_MASK_IMM ADDR=0x81 DATA=0x00 MASK=0xFB REG_WRITE_MASK_IMM ADDR=0x3D DATA=0x40 MASK=0xBF DELAY_IMM 100ms REG_WRITE_MASK_IMM ADDR=0x3D DATA=0x20 MASK=0xDF DELAY_IMM 14ms REG_WRITE_MASK_IMM ADDR=0x3D DATA=0x80 MASK=0x7F REG_WRITE_MASK_IMM ADDR=0xC3 DATA=0x80 MASK=0x7F REG_WRITE_MASK_IMM ADDR=0x082 DATA=0x00 MASK=0xF7 TRIG_MASK 0xFFFFFE5 END 2Safe: REG_WRITE_MASK_IMM ADDR=0x082 DATA=0x08 MASK=0xF7 REG_WRITE_MASK_IMM ADDR=0x3D DATA=0x00 MASK=0xDF REG_WRITE_MASK_IMM ADDR=0x3D DATA=0x00 MASK=0xBF DELAY_IMM 5ms REG_WRITE_MASK_IMM ADDR=0x3D DATA=0x00 MASK=0x7F REG_WRITE_MASK_IMM ADDR=0x82 DATA=0x10 MASK=0xEF REG_WRITE_MASK_IMM ADDR=0x2B DATA=0x00 MASK=0xFE REG_WRITE_MASK_IMM ADDR=0x81 DATA=0x04 MASK=0xFB TRIG_MASK 0xFFFFFFE END 2STANDBY: REG_WRITE_MASK_IMM ADDR=0x082 DATA=0x08 MASK=0xF7 REG_WRITE_MASK_IMM ADDR=0x3D DATA=0x00 MASK=0xDF REG_WRITE_MASK_IMM ADDR=0x3D DATA=0x00 MASK=0xBF DELAY_IMM 5ms REG_WRITE_MASK_IMM ADDR=0x3D DATA=0x00 MASK=0x7F REG_WRITE_MASK_IMM ADDR=0x82 DATA=0x10 MASK=0xEF REG_WRITE_MASK_IMM ADDR=0x2B DATA=0x00 MASK=0xFE REG_WRITE_MASK_IMM ADDR=0x81 DATA=0x04 MASK=0xFB TRIG_MASK 0xFFFFFFB END

0x0004 = 0x20 0x0005 = 0x3a 0x0006 = 0x20 0x0007 = 0x3a 0x0008 = 0x20 0x0009 = 0x1a 0x000a = 0x20 0x000b = 0x1a 0x000e = 0x41 0x000f = 0x2d 0x0010 = 0x41 0x0011 = 0x2d 0x0012 = 0xb2 0x0013 = 0xb2 0x0014 = 0x73 0x0015 = 0x73 0x0018 = 0x12 0x0019 = 0x12 0x001a = 0x12 0x001b = 0x12 0x002b = 0x01 0x002c = 0x1b 0x002d = 0x00 0x002e = 0x00 0x002f = 0x00 0x0030 = 0x00 0x0031 = 0x69 0x0032 = 0x09 0x0033 = 0x0c 0x0034 = 0x38 0x0035 = 0x08 0x0036 = 0x09 0x0037 = 0x09 0x0038 = 0x09 0x0039 = 0x0c 0x003a = 0x01 0x003c = 0x00 0x003d = 0x00 0x003e = 0x00 0x0041 = 0x55 0x0043 = 0x0c 0x0044 = 0x15 0x0045 = 0x01 0x0046 = 0x55 0x0047 = 0x55 0x0048 = 0x05 0x0049 = 0x00 0x004a = 0x00 0x004e = 0x6c 0x004f = 0xff 0x0050 = 0xff 0x0051 = 0x1b 0x0052 = 0x10 0x0053 = 0x03 0x0054 = 0xd6 0x0056 = 0x8e 0x0057 = 0xab 0x0058 = 0x09 0x0059 = 0x38 0x0078 = 0xa2 0x007b = 0x89 0x007c = 0x00 0x007d = 0xe0 0x0084 = 0x00 0x0087 = 0x00 0x0088 = 0x00 0x008a = 0x00 0x008b = 0x10 0x008e = 0x00 0x0092 = 0x00 0x00a7 = 0xb5 0x00a8 = 0x00 0x00c3 = 0x70 0x00cd = 0x10 0x00ce = 0x20 0x00cf = 0x40 0x00d0 = 0x80 0x00f0 = 0x00 0x00f1 = 0x00 0x00f2 = 0x00 0x00f3 = 0x00 0x00f4 = 0x00 0x00f5 = 0x00 0x00f6 = 0x00 0x00f7 = 0x00 0x00f8 = 0x00 0x00f9 = 0x00 0x00fe = 0x00 0x00ff = 0x00 0x0100 = 0x02 0x0101 = 0x00 0x0102 = 0x01 0x0103 = 0x02 0x0104 = 0x02 0x0105 = 0x02 0x0106 = 0x02 0x0107 = 0xff 0x0108 = 0x00 0x0109 = 0x00 0x010a = 0x54 0x010b = 0x3f 0x010c = 0x0c 0x010d = 0x33 0x010e = 0xaa 0x010f = 0x6c 0x0110 = 0x52 0x0111 = 0xca 0x0112 = 0x83 0x0113 = 0x23 0x0114 = 0x09 0x0115 = 0x18 0x0117 = 0x21 0x0118 = 0x00 0x0119 = 0x80 0x011a = 0x00 0x011b = 0x0b 0x011c = 0x16 0x011d = 0x88 0x011e = 0x88 0x011f = 0x88 0x0120 = 0x00 0x0121 = 0x05 0x0122 = 0x48 0x0123 = 0x12 0x0124 = 0x00 0x0125 = 0x02 0x0126 = 0x01 0x0127 = 0x09 0x0128 = 0x00 0x0133 = 0x0f 0x0134 = 0x00 0x0135 = 0x00 0x0136 = 0x3f 0x0137 = 0x3f 0x013f = 0x01 0x0140 = 0xc7 0x0142 = 0x00 0x0143 = 0x01 0x3000 = 0x0a 0x3001 = 0xfe 0x3002 = 0x3e 0x3003 = 0x00 0x3004 = 0x1a 0x3005 = 0x80 0x3006 = 0x02 0x3007 = 0x0d 0x3008 = 0x2a 0x3009 = 0x80 0x300a = 0x02 0x300b = 0x0d 0x300c = 0x3a 0x300d = 0x84 0x300e = 0x02 0x300f = 0x12 0x3010 = 0x4a 0x3011 = 0x88 0x3012 = 0x02 0x3013 = 0x12 0x3014 = 0x5a 0x3015 = 0x98 0x3016 = 0x20 0x3017 = 0x07 0x3018 = 0xfb 0x3019 = 0xfd 0x301a = 0xff 0x301b = 0xff 0x301c = 0xdc 0x301d = 0x82 0x301e = 0xd8 0x301f = 0x2b 0x3020 = 0xd1 0x3021 = 0x81 0x3022 = 0xd4 0x3023 = 0x3d 0x3024 = 0x8d 0x3025 = 0x1f 0x3026 = 0xdd 0x3027 = 0xb3 0x3028 = 0x48 0x3029 = 0xd0 0x302a = 0x3d 0x302b = 0xdf 0x302c = 0xc3 0x302d = 0xdf 0x302e = 0x82 0x302f = 0xb6 0x3030 = 0xe5 0x3031 = 0xff 0x3032 = 0xff 0x3033 = 0xcf 0x3034 = 0x2d 0x3035 = 0x78 0x3036 = 0xdd 0x3037 = 0xa3 0x3038 = 0xdd 0x3039 = 0xc3 0x303a = 0x28 0x303b = 0xd0 0x303c = 0x3d 0x303d = 0xde 0x303e = 0x82 0x303f = 0xd9 0x3040 = 0x2b 0x3041 = 0xd0 0x3042 = 0x81 0x3043 = 0xb5 0x3044 = 0xfe 0x3045 = 0xff 0x3046 = 0xff 0x3047 = 0xcf 0x3048 = 0x2d 0x3049 = 0x78 0x304a = 0xdd 0x304b = 0xa3 0x304c = 0xdd 0x304d = 0xc3 0x304e = 0x28 0x304f = 0xd0 0x3050 = 0x3d 0x3051 = 0xde 0x3052 = 0x82 0x3053 = 0xd9 0x3054 = 0x2b 0x3055 = 0xd0 0x3056 = 0x81 0x3057 = 0xb5 0x3058 = 0xfb 0x3059 = 0xff 0x305a = 0xff 0x305b = 0xcf 0x305c = 0x00 0x305d = 0x00 0x305e = 0x00 0x305f = 0x00 0x3060 = 0x00 0x3061 = 0x00 0x3062 = 0x00 0x3063 = 0x00 0x3064 = 0x00 0x3065 = 0x00 0x3066 = 0x00 0x3067 = 0x00 0x3068 = 0x00 0x3069 = 0x00 0x306a = 0x00 0x306b = 0x00 0x306c = 0x00 0x306d = 0x00 0x306e = 0x00 0x306f = 0x00 0x3070 = 0x00 0x3071 = 0x00 0x3072 = 0x00 0x3073 = 0x00 0x3074 = 0x00 0x3075 = 0x00 0x3076 = 0x00 0x3077 = 0x00 0x3078 = 0x00 0x3079 = 0x00 0x307a = 0x00 0x307b = 0x00 0x307c = 0x00 0x307d = 0x00 0x307e = 0x00 0x307f = 0x00 0x3080 = 0x00 0x3081 = 0x00 0x3082 = 0x00 0x3083 = 0x00 0x3084 = 0x00 0x3085 = 0x00 0x3086 = 0x00 0x3087 = 0x00 0x3088 = 0x00 0x3089 = 0x00 0x308a = 0x00 0x308b = 0x00 0x308c = 0x00 0x308d = 0x00 0x308e = 0x00 0x308f = 0x00 0x3090 = 0x00 0x3091 = 0x00 0x3092 = 0x00 0x3093 = 0x00 0x3094 = 0x00 0x3095 = 0x00 0x3096 = 0x00 0x3097 = 0x00 0x3098 = 0x00 0x3099 = 0x00 0x309a = 0x00 0x309b = 0x00 0x309c = 0x00 0x309d = 0x00 0x309e = 0x00 0x309f = 0x00 0x30a0 = 0x00 0x30a1 = 0x00 0x30a2 = 0x00 0x30a3 = 0x00 0x30a4 = 0x00 0x30a5 = 0x00 0x30a6 = 0x00 0x30a7 = 0x00 0x30a8 = 0x00 0x30a9 = 0x00 0x30aa = 0x00 0x30ab = 0x00 0x30ac = 0x00 0x30ad = 0x00 0x30ae = 0x00 0x30af = 0x00 0x30b0 = 0x00 0x30b1 = 0x00 0x30b2 = 0x00 0x30b3 = 0x00 0x30b4 = 0x00 0x30b5 = 0x00 0x30b6 = 0x00 0x30b7 = 0x00 0x30b8 = 0x00 0x30b9 = 0x00 0x30ba = 0x00 0x30bb = 0x00 0x30bc = 0x00 0x30bd = 0x00 0x30be = 0x00 0x30bf = 0x00 0x30c0 = 0x00 0x30c1 = 0x00 0x30c2 = 0x00 0x30c3 = 0x00 0x30c4 = 0x00 0x30c5 = 0x00 0x30c6 = 0x00 0x30c7 = 0x00 0x30c8 = 0x00 0x30c9 = 0x00 0x30ca = 0x00 0x30cb = 0x00 0x30cc = 0x00 0x30cd = 0x00 0x30ce = 0x00 0x30cf = 0x00 0x30d0 = 0x00 0x30d1 = 0x00 0x30d2 = 0x00 0x30d3 = 0x00 0x30d4 = 0x00 0x30d5 = 0x00 0x30d6 = 0x00 0x30d7 = 0x00 0x30d8 = 0x00 0x30d9 = 0x00 0x30da = 0x00 0x30db = 0x00 0x30dc = 0x00 0x30dd = 0x00 0x30de = 0x00 0x30df = 0x00 0x30e0 = 0x00 0x30e1 = 0x00 0x30e2 = 0x00 0x30e3 = 0x00 0x30e4 = 0x00 0x30e5 = 0x00 0x30e6 = 0x00 0x30e7 = 0x00 0x30e8 = 0x00 0x30e9 = 0x00 0x30ea = 0x00 0x30eb = 0x00 0x30ec = 0x00 0x30ed = 0x00 0x30ee = 0x00 0x30ef = 0x00 0x30f0 = 0x00 0x30f1 = 0x00 0x30f2 = 0x00 0x30f3 = 0x00 0x30f4 = 0x00 0x30f5 = 0x00 0x30f6 = 0x00 0x30f7 = 0x00 0x30f8 = 0x00 0x30f9 = 0x00 0x30fa = 0x00 0x30fb = 0x00 0x30fc = 0x00 0x30fd = 0x00 0x30fe = 0x00 0x30ff = 0x00 0x3100 = 0x00 0x3101 = 0x00 0x3102 = 0x00 0x3103 = 0x00 0x3104 = 0x00 0x3105 = 0x00 0x3106 = 0x00 0x3107 = 0x00 0x3108 = 0x00 0x3109 = 0x00 0x310a = 0x00 0x310b = 0x00 0x310c = 0x00 0x310d = 0x00 0x310e = 0x00 0x310f = 0x00 0x3110 = 0x00 0x3111 = 0x00 0x3112 = 0x00 0x3113 = 0x00 0x3114 = 0x00 0x3115 = 0x00 0x3116 = 0x00 0x3117 = 0x00 0x3118 = 0x00 0x3119 = 0x00 0x311a = 0x00 0x311b = 0x00 0x311c = 0x00 0x311d = 0x00 0x311e = 0x00 0x311f = 0x00 0x3120 = 0x00 0x3121 = 0x00 0x3122 = 0x00 0x3123 = 0x00 0x3124 = 0x00 0x3125 = 0x00 0x3126 = 0x00 0x3127 = 0x00 0x3128 = 0x00 0x3129 = 0x00 0x312a = 0x00 0x312b = 0x00 0x312c = 0x00 0x312d = 0x00 0x312e = 0x00 0x312f = 0x00 0x3130 = 0x00 0x3131 = 0x00 0x3132 = 0x00 0x3133 = 0x00 0x3134 = 0x00 0x3135 = 0x00 0x3136 = 0x00 0x3137 = 0x00 0x3138 = 0x00 0x3139 = 0x00 0x313a = 0x00 0x313b = 0x00 0x313c = 0x00 0x313d = 0x00 0x313e = 0x00 0x313f = 0x00 0x3140 = 0x00 0x3141 = 0x00 0x3142 = 0x00 0x3143 = 0x00 0x3144 = 0x00 0x3145 = 0x00 0x3146 = 0x00 0x3147 = 0x00 0x3148 = 0x00 0x3149 = 0x00 0x314a = 0x00 0x314b = 0x00 0x314c = 0x00 0x314d = 0x00 0x314e = 0x00 0x314f = 0x00 0x3150 = 0x00 0x3151 = 0x00 0x3152 = 0x00 0x3153 = 0x00 0x3154 = 0x00 0x3155 = 0x00 0x3156 = 0x00 0x3157 = 0x00 0x3158 = 0x00 0x3159 = 0x00 0x315a = 0x00 0x315b = 0x00 0x315c = 0x00 0x315d = 0x00 0x315e = 0x00 0x315f = 0x00 0x3160 = 0x00 0x3161 = 0x00 0x3162 = 0x00 0x3163 = 0x00 0x3164 = 0x00 0x3165 = 0x00 0x3166 = 0x00 0x3167 = 0x00 0x3168 = 0x00 0x3169 = 0x00 0x316a = 0x00 0x316b = 0x00 0x316c = 0x00 0x316d = 0x00 0x316e = 0x00 0x316f = 0x00 0x3170 = 0x00 0x3171 = 0x00 0x3172 = 0x00 0x3173 = 0x00 0x3174 = 0x00 0x3175 = 0x00 0x3176 = 0x00 0x3177 = 0x00 0x3178 = 0x00 0x3179 = 0x00 0x317a = 0x00 0x317b = 0x00 0x317c = 0x00 0x317d = 0x00 0x317e = 0x00 0x317f = 0x00 0x3180 = 0x00 0x3181 = 0x00 0x3182 = 0x00 0x3183 = 0x00 0x3184 = 0x00 0x3185 = 0x00 0x3186 = 0x00 0x3187 = 0x00 0x3188 = 0x00 0x3189 = 0x00 0x318a = 0x00 0x318b = 0x00 0x318c = 0x00 0x318d = 0x00 0x318e = 0x00 0x318f = 0x00 0x3190 = 0x00 0x3191 = 0x00 0x3192 = 0x00 0x3193 = 0x00 0x3194 = 0x00 0x3195 = 0x00 0x3196 = 0x00 0x3197 = 0x00 0x3198 = 0x00 0x3199 = 0x00 0x319a = 0x00 0x319b = 0x00 0x319c = 0x00 0x319d = 0x00 0x319e = 0x00 0x319f = 0x00 0x31a0 = 0x00 0x31a1 = 0x00 0x31a2 = 0x00 0x31a3 = 0x00 0x31a4 = 0x00 0x31a5 = 0x00 0x31a6 = 0x00 0x31a7 = 0x00 0x31a8 = 0x00 0x31a9 = 0x00 0x31aa = 0x00 0x31ab = 0x00 0x31ac = 0x00 0x31ad = 0x00 0x31ae = 0x00 0x31af = 0x00 0x31b0 = 0x00 0x31b1 = 0x00 0x31b2 = 0x00 0x31b3 = 0x00 0x31b4 = 0x00 0x31b5 = 0x00 0x31b6 = 0x00 0x31b7 = 0x00 0x31b8 = 0x00 0x31b9 = 0x00 0x31ba = 0x00 0x31bb = 0x00 0x31bc = 0x00 0x31bd = 0x00 0x31be = 0x00 0x31bf = 0x00 0x31c0 = 0x00 0x31c1 = 0x00 0x31c2 = 0x00 0x31c3 = 0x00 0x31c4 = 0x00 0x31c5 = 0x00 0x31c6 = 0x00 0x31c7 = 0x00 0x31c8 = 0x00 0x31c9 = 0x00 0x31ca = 0x00 0x31cb = 0x00 0x31cc = 0x00 0x31cd = 0x00 0x31ce = 0x00 0x31cf = 0x00 0x31d0 = 0x00 0x31d1 = 0x00 0x31d2 = 0x00 0x31d3 = 0x00 0x31d4 = 0x00 0x31d5 = 0x00 0x31d6 = 0x00 0x31d7 = 0x00 0x31d8 = 0x00 0x31d9 = 0x00 0x31da = 0x00 0x31db = 0x00 0x31dc = 0x00 0x31dd = 0x00 0x31de = 0x00 0x31df = 0x00 0x31e0 = 0x00 0x31e1 = 0x00 0x31e2 = 0x00 0x31e3 = 0x00 0x31e4 = 0x00 0x31e5 = 0x00 0x31e6 = 0x00 0x31e7 = 0x00 0x31e8 = 0x00 0x31e9 = 0x00 0x31ea = 0x00 0x31eb = 0x00 0x31ec = 0x00 0x31ed = 0x00 0x31ee = 0x00 0x31ef = 0x00 0x31f0 = 0x00 0x31f1 = 0x00 0x31f2 = 0x00 0x31f3 = 0x00 0x31f4 = 0x00 0x31f5 = 0x00 0x31f6 = 0x00 0x31f7 = 0x00 0x31f8 = 0x00 0x31f9 = 0x00 0x31fa = 0x00 0x31fb = 0x00 0x31fc = 0x00 0x31fd = 0x00 0x31fe = 0x00 0x31ff = 0x00 0x0405 = 0x00 0x0409 = 0xbf