Other Parts Discussed in Thread: UC2842, UCC28C42

Hi All!

I have a few queries regarding UCC2807 datasheet.

1. The datasheet does not mention the delay between the detection of current limit (at CS pin) and reset of PWM signal. What is the delay for the UCC2807-1.

2. In the datasheet in current sense section, there is a parameter COMP to CS Offset. Can you please help me to understand this parameter?

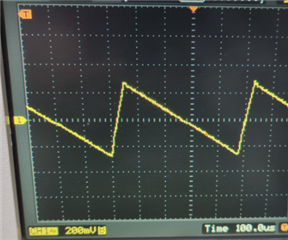

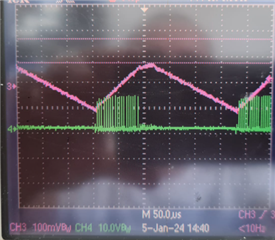

3. We are using UCC2807 to control forward converter in peak current mode control. At noload there the converter exhibit burst mode/cycle skipping operation. However, I want to know, how the control chip determines/calculates the upper and lower threshold of voltage to initiate/stop burst mode.

Thank you!

Best Regards

Samir