Hi

We use the LP8764-Q1 on our automotive project.

the condition is:

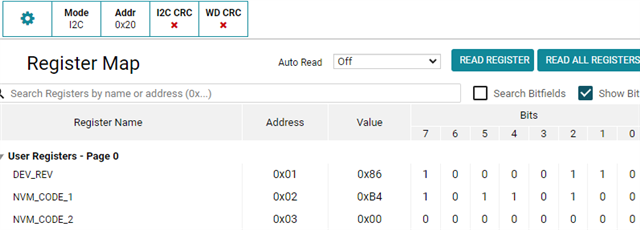

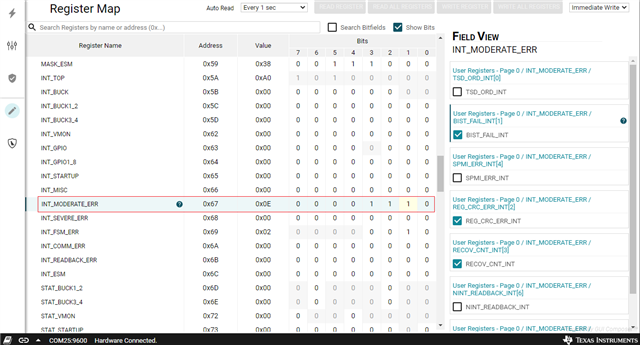

1. the RECOV_CNT_REG_2 (RECOV_CNT_THR) value is set to 0.

2. we turn the GENERAL_REG_1(REG_CRC_EN) to the "register CRC enable".

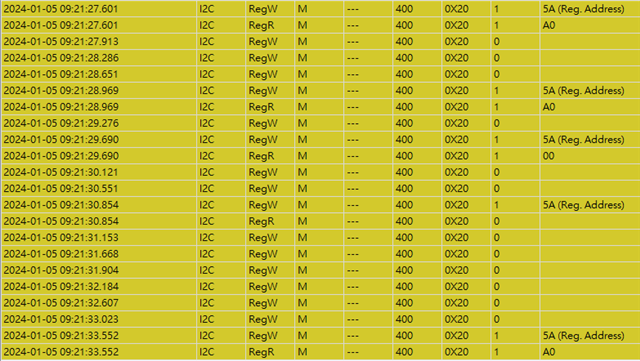

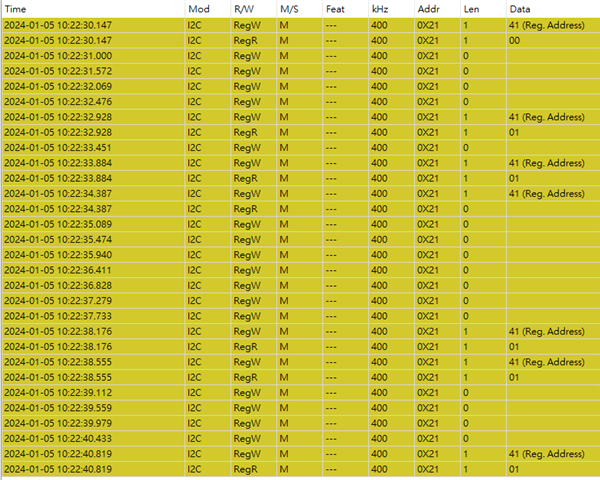

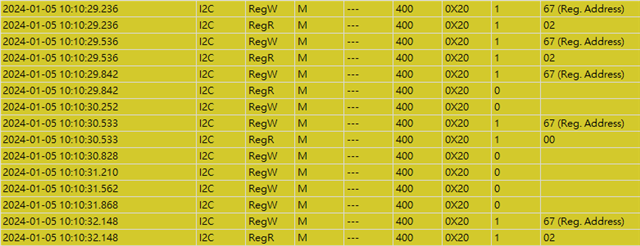

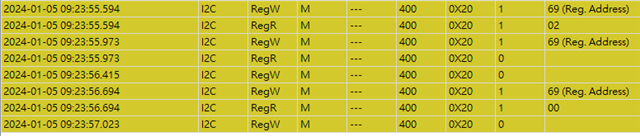

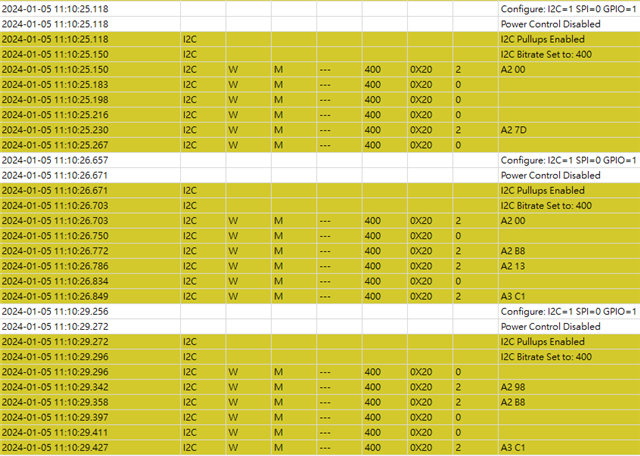

We use the Linux command to upgrade the PMIC firmware through the I2C interface. we do the power cycle after the program is finished, then try to do the CRC write. we found that the PMIC is not workable.

We know the procedure is incorrect, currently. the correct procedure should be the program the chip, then do the CRC, and the last step is the power cycle.

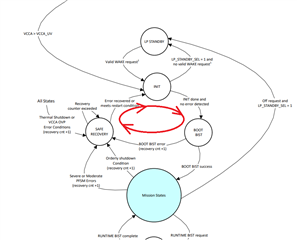

Is the PMIC working in the infinity initial loop state? do we have any way to stop it, and then use the Tool to access the chip?

Does the recovery count mean the RECOV_CNT_REG_2 register (RECOV_CNT_THR)?

If it is, we set the value to 0. seems the value 0 means no limit.

Is my understanding correct? do we have any way to change the stage to the SAFE RECOVERY stage?

Chris