Hi all,

I have used the IC "LM5148-Q1" for the design of the buck converter, where I have calculated all the values according to the IC datasheet also verified with the support Excel file provided. Every thing looks good according to the calculation but I have an re-occurring issue that the converter output voltage is dipping with the addition of the load. the line regulation is fine i.e., at a fixed load the voltage variation is minimal but for different loads the output voltage is changing.

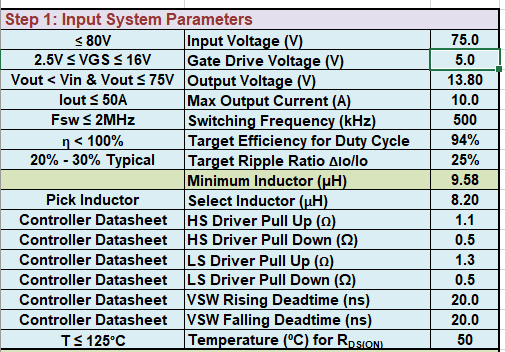

Here are my design considerations:

Input Voltage range : 40V - 60V

Output Voltage : 13.8V

Output Current : 10A (Max load)

Switching Frequency : 500kHz to 600kHz

Inductor Current Ripple : 25% of Max output current

I am trying to find the losses at different load conditions but they are not matching the theoretical losses, so I went through the "SYNC-BUCK-FET-LOSS-CALC MOSFET power loss calculator for synchronous buck converter applications" Losses calculation Macro sheet. But I am not able to get the MOSFET selection correctly, even though I am choosing the voltage as 80V (input Voltage).

Input parameters:

But the appropriate MOSFET selection is not available. Can you please guide through how to get the proper MOSFET selection.

Thanks

Mahankali Nikhilindu Kasyap