Hello,

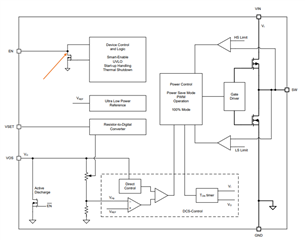

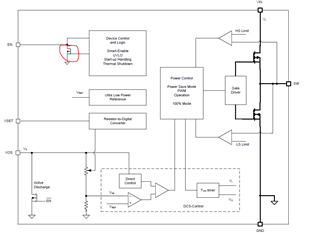

I wonder if a resistor is needed between VIN and EN, since internal FET driven by UVLO/Thermal Shutdown will pull the line directly to GND in case of failure event:

In typical application shown in WEBENCH, VIN and EN are shorted so the device will be enabled as long as VIN is above the UVLO threshold. Without resistor between VIN and EN, there won't flow a short circuit current if FET is enabled by UVLO or Thermal Shutdown?

Best regards