- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi engineer:

about power design issues for TPS6287X-Q1:

Thanks

Johnsin Tao

Hi Johnsin,

Thanks for reaching out to us.

Please see my comments on your queries below. If there are unclear items, feel free to highlight.

How is the adjustment speed evaluated? --> Can you clarify this item? Do you mean the time it takes for the Vout to change from the default value to the new setting?

2. In cascade mode, do we only need to connect the I2C interface of the Primary? How is the diagnosis of the Secondary device (OV, UV, OC, OT) achieved? --> Yes, only the I2C interface of the Primary device needs to be connected to the SoC while the SCL and SDA of the secondary device is connected to GND. In this configuration, there's no diagnostic on the secondary device. Does your customer needs to monitor the status of the secondary device?

3. In cascade mode, what is the duty cycle of the synchronous clock signal output from the SYNC pin? Is it dynamically adjustable? --> If the SYNC pin of the primary device is tied to VIN, the SYNC_OUT follows the internal oscillator set (both the duty cycle of ~50% and the frequency) by RFSEL .

On the other hand, if the SYNC pin (primary device) is connected to an external clock, the duty cycle and frequency of the SYNC_OUT pin is dictated by input on the SYNC. In this case, switching frequency of the primary and secondary devices can be dynamically adjustable.

4. Can you please provide the power calculation table for TPS6287X-Q1? --> Please use the Webench for power calculation.

https://webench.ti.com/power-designer/switching-regulator/customize/217?VinMin=2.7&VinMax=6&O1V=0.75&O1I=6&base_pn=TPS62870-Q1&AppType=None&Flavor=None&op_TA=30&origin=pf_panel&lang_chosen=en-US&optfactor=3&Topology=Buck&flavor=None&VoltageOption=None

Best regards,

Excel

Hi Excel,

The following questions have been raised by our team. Additionally, two further points of clarification are as follows:

1.How is the adjustment speed evaluated? --> Can you clarify this item? Do you mean the time it takes for the Vout to change from the default value to the new setting?

RE:Yes,We are interested in knowing the adjustment time after a change in voltage. For instance, in a scenario where three devices are cascaded to supply power to the SOC, how long does it take for the last chip to respond? How many cycles? or ms?us?

2. In cascade mode, do we only need to connect the I2C interface of the Primary? How is the diagnosis of the Secondary device (OV, UV, OC, OT) achieved? --> Yes, only the I2C interface of the Primary device needs to be connected to the SoC while the SCL and SDA of the secondary device is connected to GND. In this configuration, there's no diagnostic on the secondary device. Does your customer needs to monitor the status of the secondary device?

RE:Yes,From the perspective of functional safety, the secondary power source also needs to be monitored.

Hi Johnsin,

For item #1, I need me until Friday to check on this item. On the other hand, please see my response on the other items below.

2. In cascade mode, do we only need to connect the I2C interface of the Primary? How is the diagnosis of the Secondary device (OV, UV, OC, OT) achieved? --> Yes, only the I2C interface of the Primary device needs to be connected to the SoC while the SCL and SDA of the secondary device is connected to GND. In this configuration, there's no diagnostic on the secondary device. Does your customer needs to monitor the status of the secondary device?

RE:Yes,From the perspective of functional safety, the secondary power source also needs to be monitored.

[Excel] In stacked configuration, the SDA and SCL pins of the secondary device/s need to be tied to GND. Hence, the customer will not be able to monitor its status. Anyway, the customer can use a separate supervisory IC to monitor slaves IC's.

Best regards,

Excel

Hello Johnsin,

Apologies for the late response. Please see my answer to item #1 highlighted in blue.

1.How is the adjustment speed evaluated? --> Can you clarify this item? Do you mean the time it takes for the Vout to change from the default value to the new setting?

RE:Yes,We are interested in knowing the adjustment time after a change in voltage. For instance, in a scenario where three devices are cascaded to supply power to the SOC, how long does it take for the last chip to respond? How many cycles? or ms?us?

[Excel] Ideally, all the devices (primary and secondary ICs) will adjust the Vout almost simultaneously because all the COMP pins are tied together. (COMP pin is the output of the error amplifier, which compares VOUT to VREF heavily influence the duty cycle).

Let me know if you have open queries.

Best regards,

Excel

Hello Johnsin,

Just a gentle reminder.

Do stil have other questions? If not, can you kindly close the thread?

Thank you.

Best regards,

Excel

Hi,Excel,

Are there any requirements for the routing of the VCOMP pin? This pin connects to the second/third cascaded chip, so the routing should not be too short. If used, this line is quite important, as even a slight interference can affect the output voltage. Do we really not need to add a capacitor or something at the end of the cascade?

Also, for the second/third cascaded chips, we can't test loop compensation, and there's nowhere to adjust it. With this cascading design, we only debug the first chip, and if there are parameter changes, the other two will follow suit.

Tks!

Hello Chunyang,

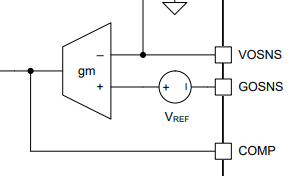

You are correct. The COMP traces of the secondary converters need to be taken care of. The PCB tracks should be as short as possible and away from noisy or switching nodes or traces. The 10pF across COMP and GOSNS pins on the slave/cascade converters are use to suppress the high frequency noise from the external circuit.

I think it still possible to check the loop stability of the secondary devices if the customers want to (see figure below). But of course, if the primary device is stable, the secondary devices should have similar loop stability performance.

I hope I was able to address your queries.

Best regards,

Excel

Hello Chunyang,

I'm closing this thread. If you further questions, you add comments to re-open it.

Best regards,

Excel