Customer are conducting a 24V momentary power failure test on the TPS38A010122 circuit, and the conditions and phenomena are as follows.

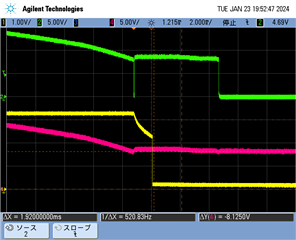

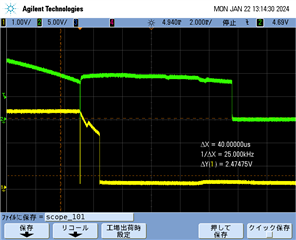

・VDD: 24V (ch4, Red)

・SENSE1/2: 8.13V divided from 24VDD

・CTR1/2: 0.1μF

・CTS1/2:Open

・/RESET1: Pull up from 24VDD (ch1, Yellow)

・/RESET2: Pull up from 3.3V of another system (ch2, Green)

As shown in the waveform, when 24VDD is momentarily dropped, either reset output drops and then rises again.

(The waveform is /RESET1, but sometimes occurs at /RESET2)

Incidentally, the same result is obtained even if the momentary power failure time is 50μs (> tcs).

There are three questions below.

① Is there a way to avoid this behavior where it drops for a moment and then rises again?

②What is the cause of this behavior?

I am guessing that wraparound is occurring from one side of the Reset output, is this correct?

③Is it not allowed to use VDD and SENSE1/2 on the same power line?

Best regards,

Satoshi