Hello,

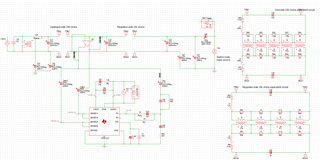

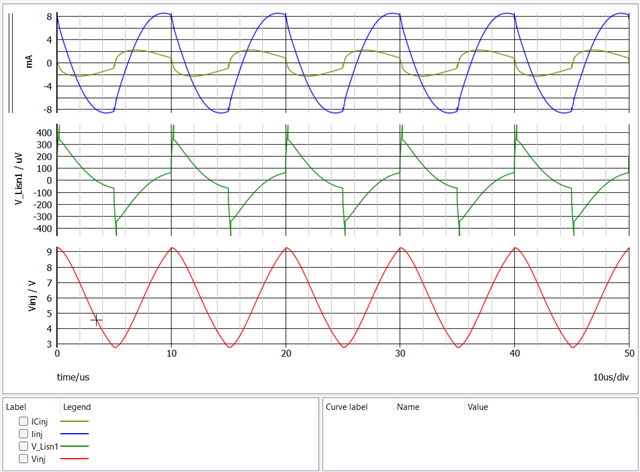

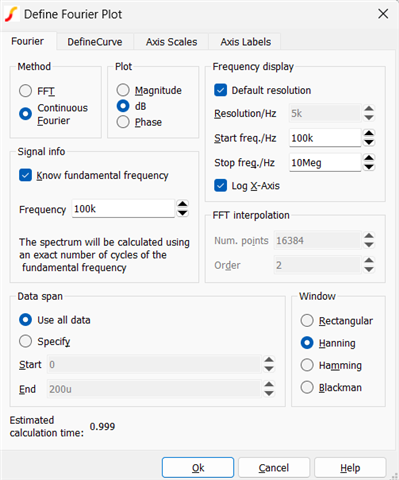

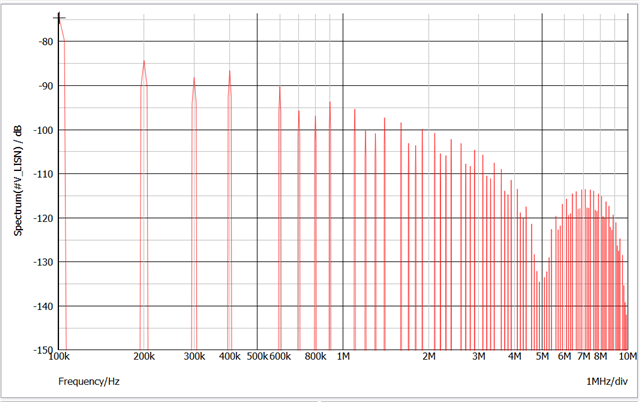

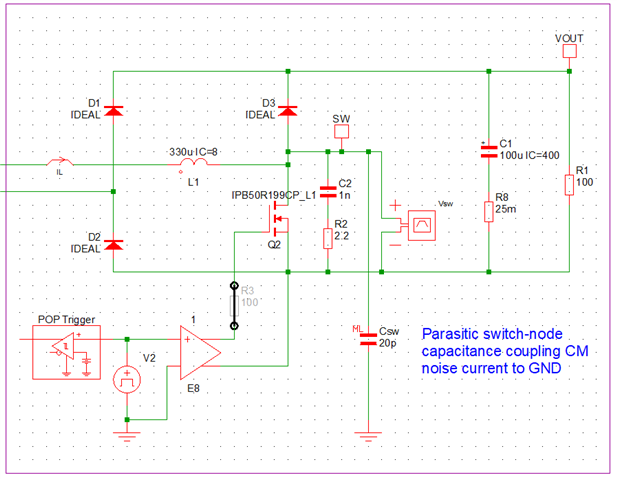

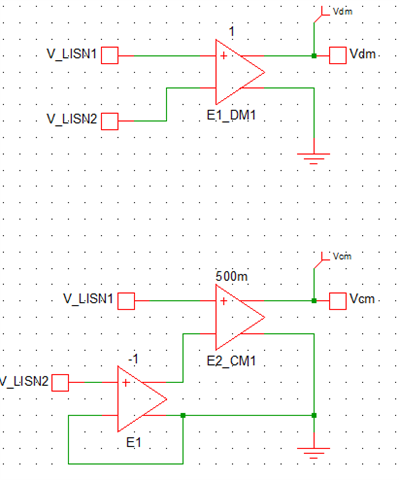

I believe that this a question for Timothy Hegarty. I am trying to use SIMPLIS model for TPSF12C1 (TPSF12C1-Q1 single-phase AEF circuit.sxsch) in more realistic circuit which includes LISN, Line impedance and PFC stage, but this IC does not work. Unfortunately I cannot attach my simulation file to this message. It looks as IC voltage saturated to Vdd. But increases of Vdd does not help. I am using all components from your original circuit. When I investigated your original file it also shows strange behaviour. When I placed voltage controlled voltage source between the lines and Csen1 & Csen2 (E2 enabled , R1 & R2 disabled )this IC does not work even all signals absolutely the same as in original circuit (E2 disabled, R1 & R2 enabled) See pic below. Could you, please, help with this problem. Also can PSPICE encrypted model for this IC work with Simetrix?

Regards.

Lev